# Microcomputer Components

8-Bit CMOS Microcontroller

C517A

Ritio Sernic onductor

|                                      | C517A Data Sheet                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Revision Hi                          | story :                                                 | 01.99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Previous Re                          | leases :                                                | 08.97 (Original Version)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Page<br>(previous<br>version)        | Page<br>(new<br>version)                                | Subjects (changes since last revision)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| All sections 2 2 2 to 3 5 5 47 48 49 | All sections<br>2<br>2<br>2<br>5<br>6<br>50<br>50<br>52 | $V_{\rm CC}$ is changed to $V_{\rm DD}$ and $I_{\rm CC}$ is changed to $I_{\rm DD}$ . "with wake-up capability through INT0 pin" is removed. P-LCC-84 package is added under the feature list. Table 1; deleted and replaced by "Ordering Information" paragraph "Additional Literature"; deleted. Figure 4; added. Table 1; modified, column "P-LCC-84" is added. "or by a short low pulse at pin P3.2/INT0" is removed. "Short low pulse at pin P3.2/INT0" is removed. "Absolute Maximum Ratings" is changed to tabular form. |  |  |  |  |  |

| 49<br>50<br>51<br>53<br>55<br>62     | 52<br>52<br>53<br>54<br>56<br>58<br>65<br>69            | Fifth line; "During overload conditions" changed to "During absolute maximum rating conditions". "Operating Conditions" is added. " $V_{\rm CC}$ = 5 V + 10% " is replaced by "(Operating Conditions apply)". Notes (7); modified. " $V_{\rm CC}$ = 5 V + 10% " is replaced by "(Operating Conditions apply)". " $V_{\rm CC}$ = 5 V + 10% " is replaced by "(Operating Conditions apply)". First line; "C517A-1RM" is replaced by "C517A-4RM/4RN" Figure 38; added.                                                             |  |  |  |  |  |

#### Edition 01.99

This edition was realized using the software system FrameMaker□.

Published by : Siemens AG, Semiconductor Group, Product Definition 8-Bit Microcontroller Components, Balanstraße 73, D-81541 München .

Siemens AG 01.99, All Rights Reserved.

"Enhanced Hooks Technology" is a trademark and patent of Metalink Corporation, licensed to Siemens.

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide.

Due to technical requirements components may contain dangerous substances. For information on the type in question please contact your nearest Siemens Office, Components Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you - get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have ti invoice you for any costs incurred.

## 8-Bit CMOS Microcontroller

C517A

#### **Advance Information**

- Full upward compatibility with SAB 80C517A/83C517A-5

- Up to 24 MHz external operating frequency

- 500 ns instruction cycle at 24 MHz operation

- Superset of the 8051 architecture with 8 datapointers

- On-chip emulation support logic (Enhanced Hooks Technology TM)

- 32K byte on-chip ROM (with optional ROM protection)

- alternatively up to 64K byte external program memory

- Up to 64K byte external data memory

- 256 byte on-chip RAM

- Additional 2K byte on-chip RAM (XRAM)

- Seven 8-bit parallel I/O ports

- · Two input ports for analog/digital input

(further features are on next page)

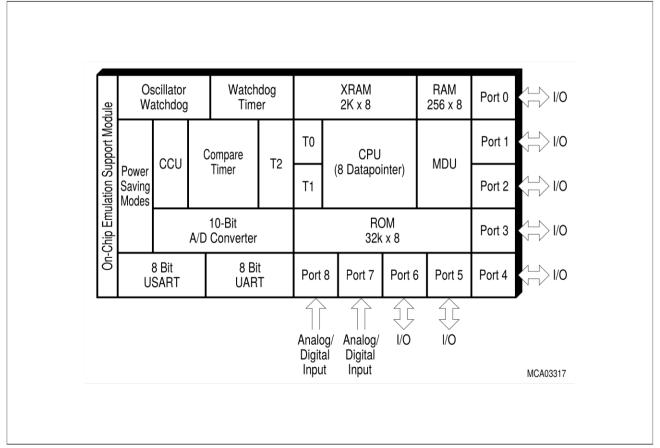

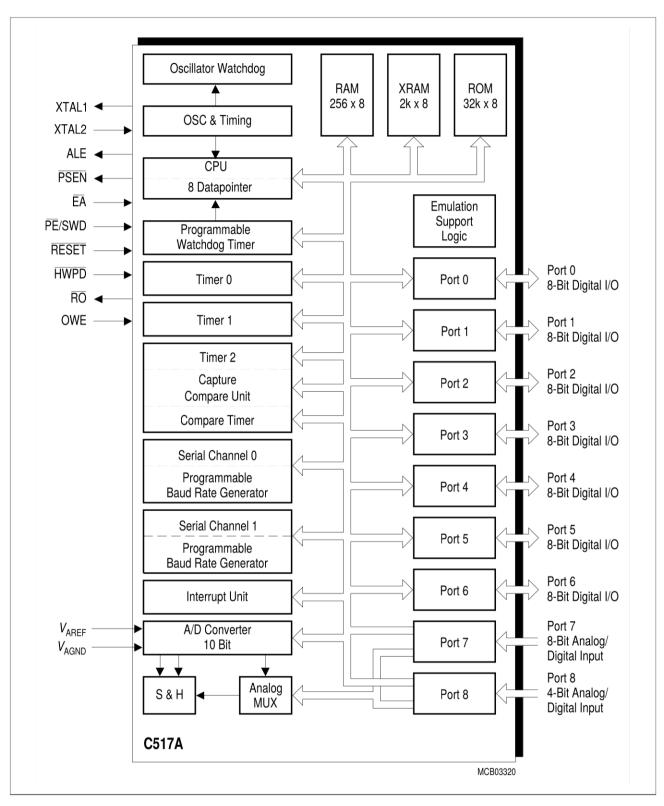

Figure 1 C517A Functional Units

## Features (continued):

- Two full duplex serial interfaces (USART)

- 4 operating modes, fixed or variable baud rates

- programmable baud rate generators

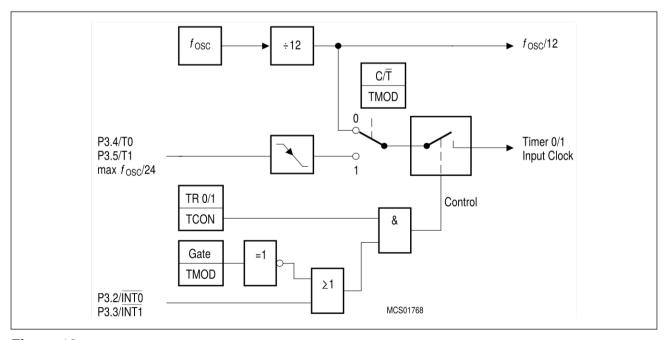

- Four 16-bit timer/counters

- Timer 0 / 1 (C501 compatible)

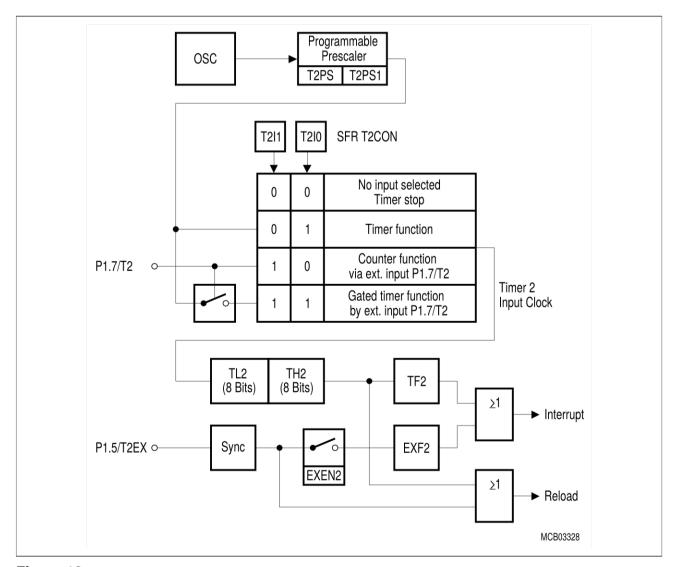

- Timer 2 for 16-bit reload, compare, or capture functions

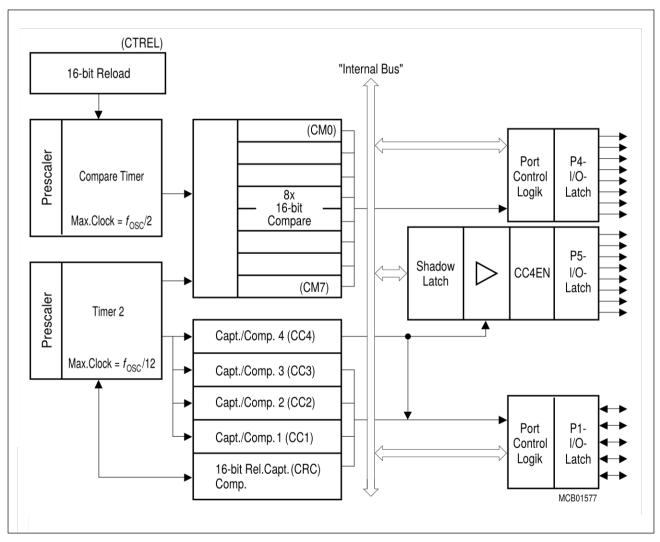

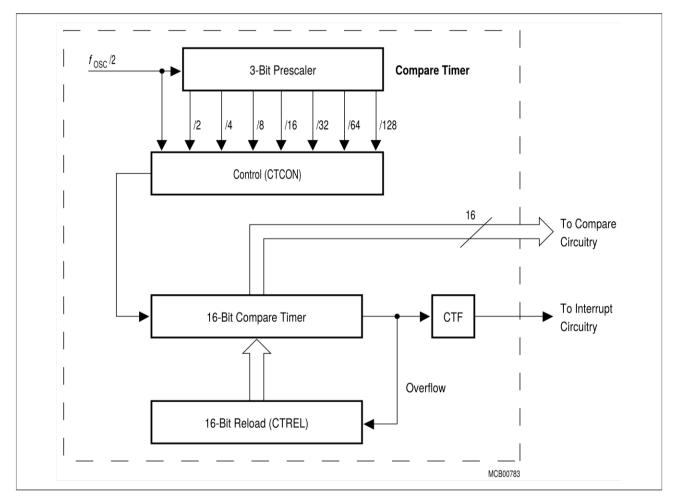

- Compare timer for compare/capture functions

- Powerful 16-bit compare/capture unt (CCU) with up to 21 high-speed or PWM output channels and 5 capture inputs

- 10-bit A/D converter

- 12 multiplexed analog inputs

- Built-in self calibration

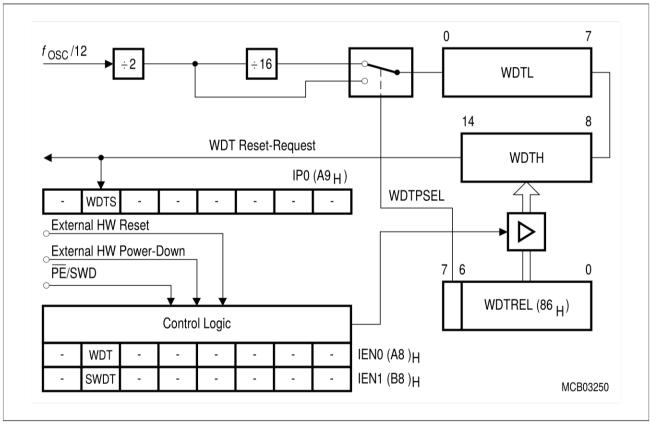

- · Extended watchdog facilities

- 15-bit programmable watchdog timer

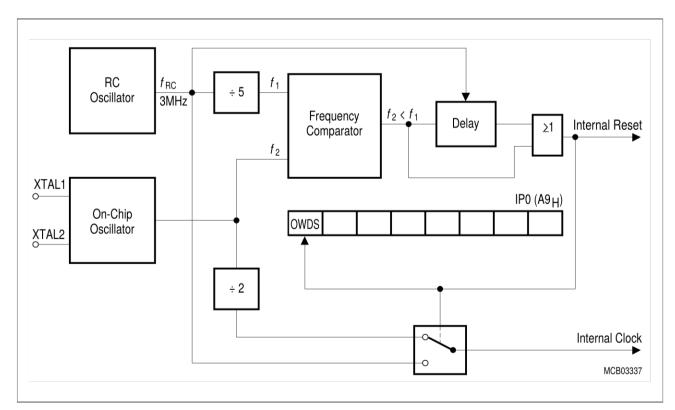

- Oscillator watchdog

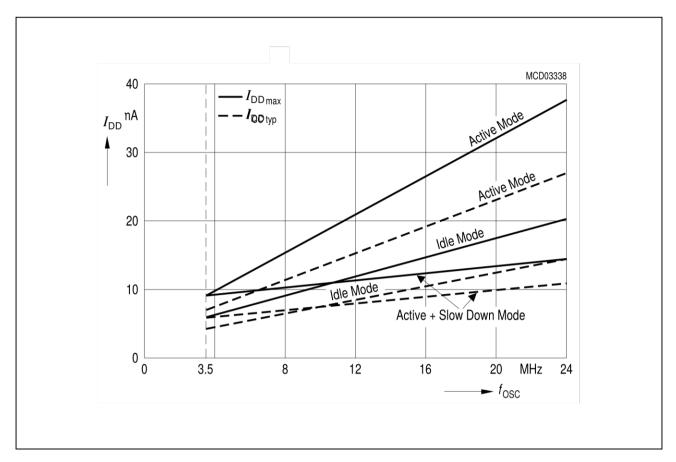

- Power saving modes

- Slow down mode

- Idle mode (can be combined with slow down mode)

- Software power-down mode

- Hardware power-down mode

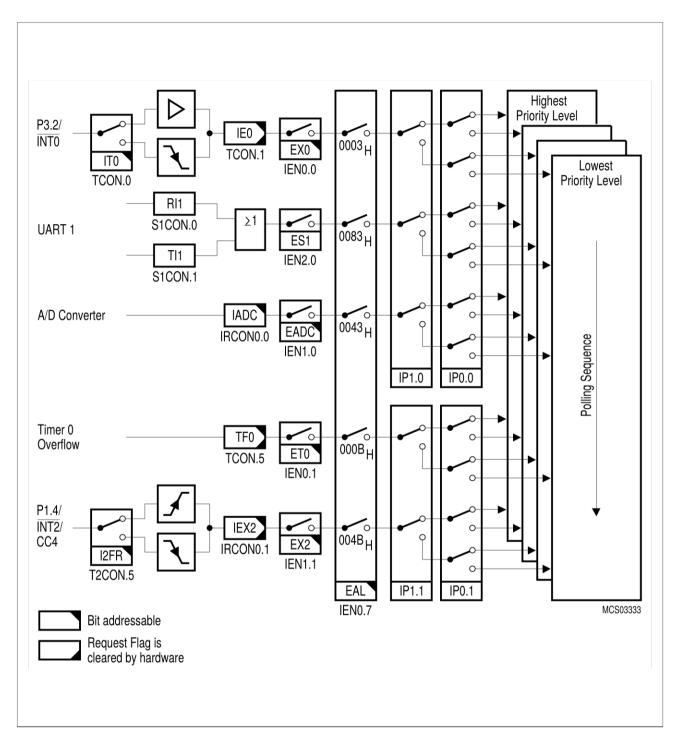

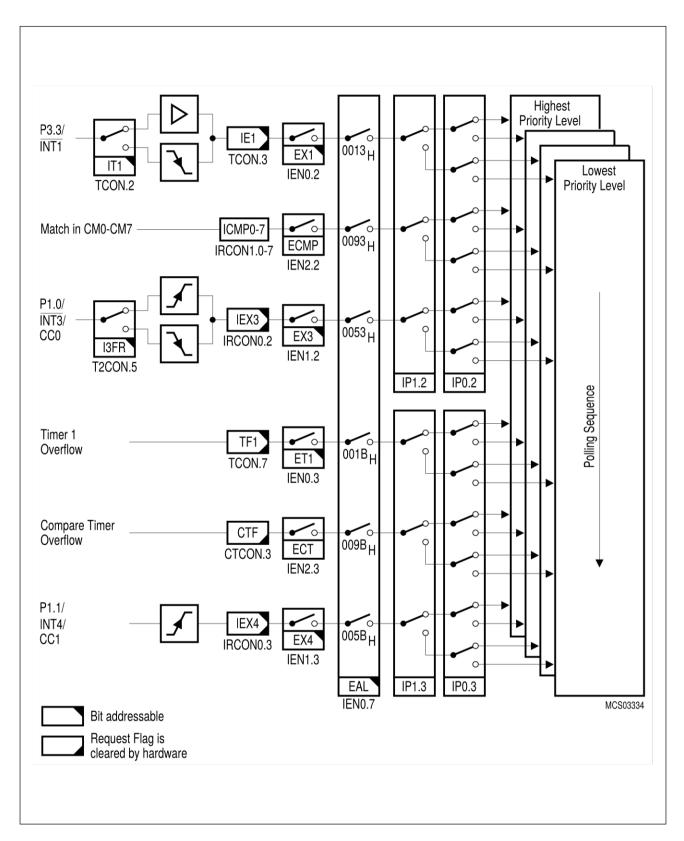

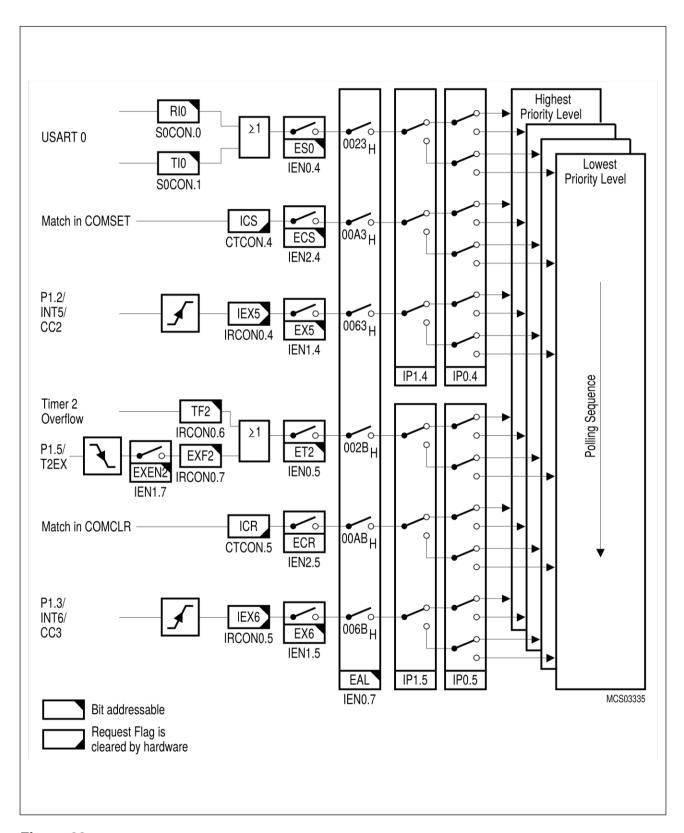

- 17 interrupt sources (7 external, 10 internal) selectable at 4 priority levels

- P-MQFP-100 and P-LCC-84 packages

• Temperature Ranges : SAB-C517A  $T_A = 0$  to 70 °C

SAF-C517A  $T_A = -40 \text{ to } 85 \text{ °C}$ SAH-C517A  $T_A = -40 \text{ to } 110 \text{ °C}$

## **Ordering Information**

The ordering code for Siemens microcontrollers provides an exact reference to the required product. This ordering code identifies:

- · the derivative itself, i.e. its function set

- the specified temperature range

- the package and the type of delivery.

For the available ordering codes for the C517A please refer to the

"Product Information Microcontrollers", which summarizes all available microcontroller variants.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

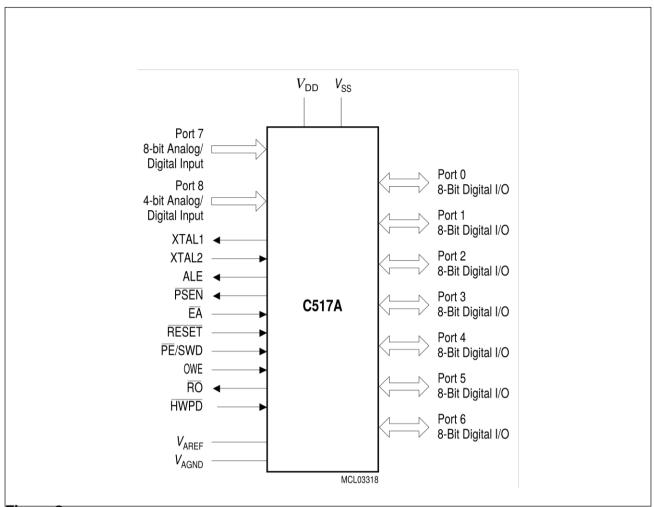

Figure 2 Logic Symbol

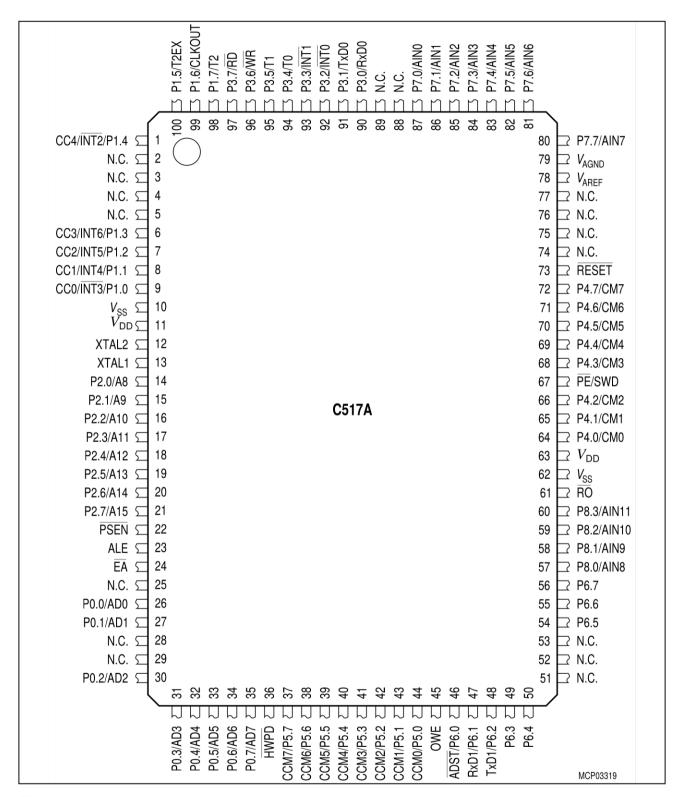

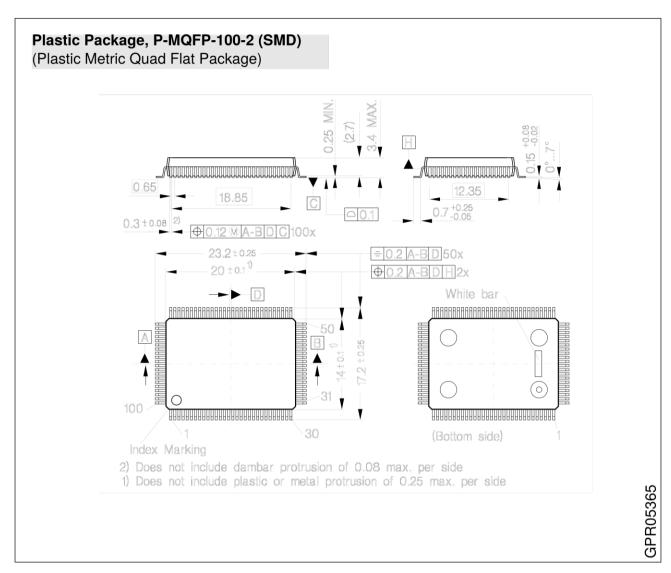

Figure 3

Pin Configuration P-MQFP-100 Package (Top View)

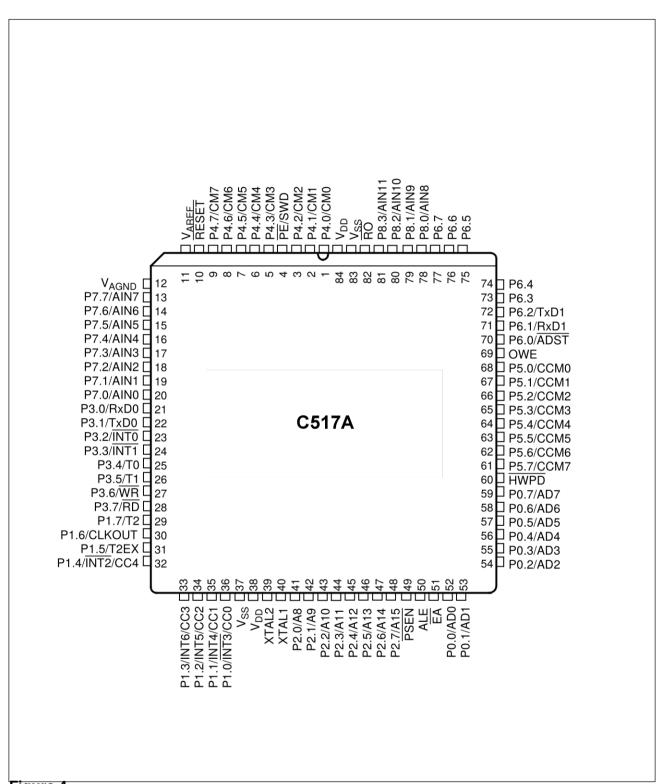

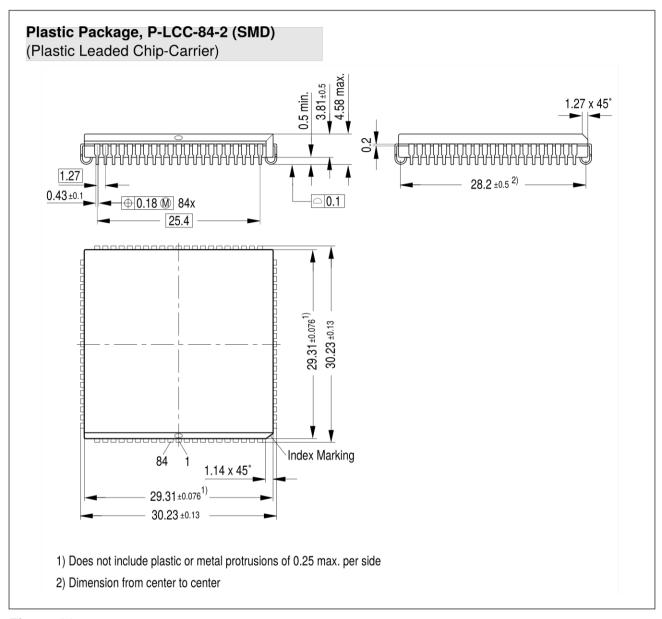

Figure 4

Pin Configuration P-LCC-84 Package (Top View)

Table 1

Pin Definitions and Functions

| Symbol      | Pin Number         |                        | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |  |

|-------------|--------------------|------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|             | P-MQFP-100         | P-LCC-84               | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |

| P1.0 - P1.7 | 9 - 6, 1, 100 - 98 | 36 - 29                | I/O   | is an 8-bit quasi-bidirectional I/O port with internal pullup resistors. Port 1 pins that have 1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 1 pins being externally pulled low will source current ( <i>I</i> <sub>IL</sub> , in the DC characteristics) because of the internal pullup resistors. The port is used for the low-order address byte during program verification. Port 1 also contains the interrupt, timer, clock, capture and compare pins that are used by various options. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate (excep when used for the compare functions). The secondary functions are assigned to the port |    |  |

|             | 9                  | 36                     |       | 1 pins as follows: P1.0 / INT3 / CC0 Interrupt 3 input / compare 0 output / capture 0 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | /  |  |

|             | 8                  | 35                     |       | P1.1 / INT4 / CC1 Interrupt 4 input / compare 1 output / capture 1 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /  |  |

|             | 7                  | 34                     |       | P1.2 / INT5 / CC2 Interrupt 5 input / compare 2 output / capture 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /  |  |

|             | 6                  | 33                     |       | P1.3 / INT6 / CC3 Interrupt 6 input / compare 3 output / capture 3 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /  |  |

|             | 1                  | 32                     |       | P1.4 / INT2 / CC4 Interrupt 2 input / compare 4 output / capture 4 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /  |  |

|             | 100                | 31 P1.5 / T2EX Timer 2 |       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ut |  |

|             | 99<br>98           | 30<br>29               |       | P1.6 / CLKOUT System clock outp<br>P1.7 / T2 Counter 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ut |  |

<sup>\*)</sup> I = Input, O = Output

Table 1

Pin Definitions and Functions (cont'd)

| Symbol          | Pin N      | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------|------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | P-MQFP-100 | P-LCC-84 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| V <sub>SS</sub> | 10, 62     | 37, 83   | _     | Ground (0V) during normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| $V_{DD}$        | 11, 63     | 38, 84   | -     | Supply voltage during normal, idle, and power down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

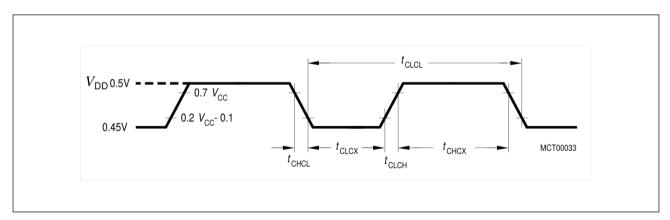

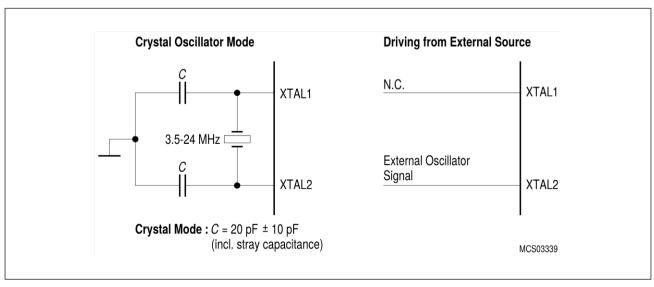

| XTAL2           | 12         | 39       | _     | is the input to the inverting oscillator amplifier and input to the internal clock generator circuits.  To drive the device from an external clock source, XTAL2 should be driven, while XTAL1 is left unconnected. Minimum and maximum high and low times as well as rise fall times specified in the AC characteristics must be observed.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| XTAL1           | 13         | 40       | _     | XTAL1 is the output of the inverting oscillator amplifier. This pin is used for the oscillator operation with crystal or ceramic resonator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

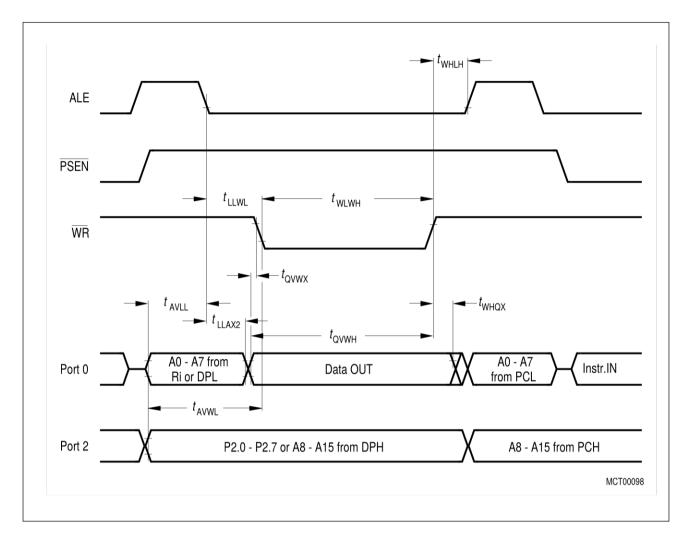

| P2.0 - P2.7     | 14 - 21    | 41 - 48  | I/O   | is an 8-bit quasi-bidirectional I/O port with internal pullup resistors. Port 2 pins that have 1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 2 pins being externally pulled low will source current ( <i>I</i> <sub>IL</sub> , in the DC characteristics) because of the internal pullup resistors. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application it uses strong internal pullup resistors when issuing 1's. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 issues the contents of the P2 special function register. |  |

<sup>\*)</sup> I = Input O = Output

Table 1

Pin Definitions and Functions (cont'd)

| Symbol      | Pin Number         |          | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------|--------------------|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | P-MQFP-100         | P-LCC-84 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

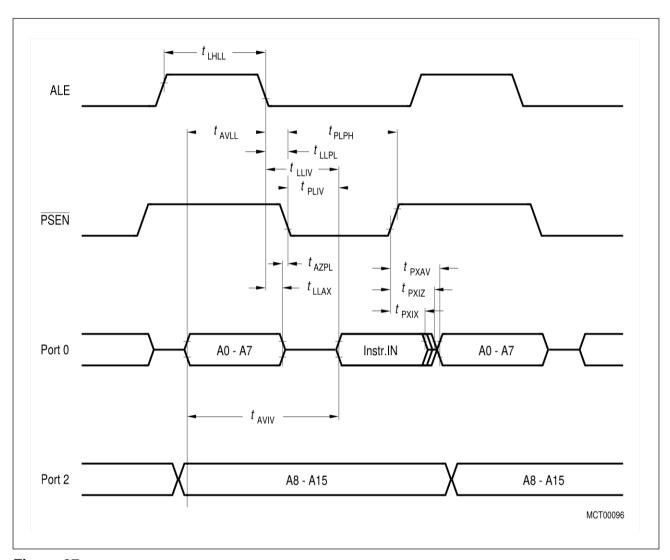

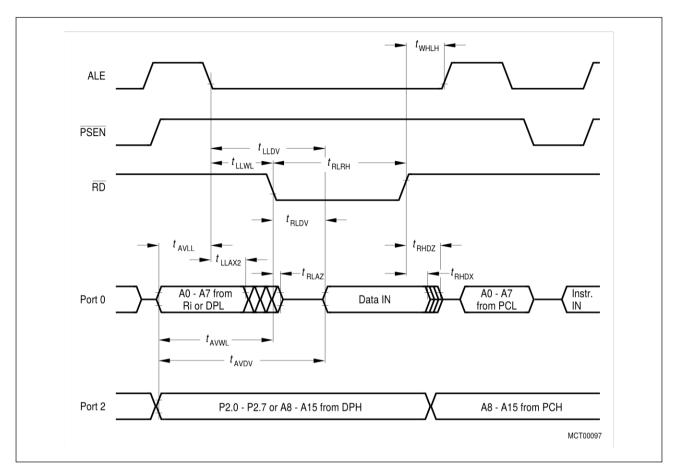

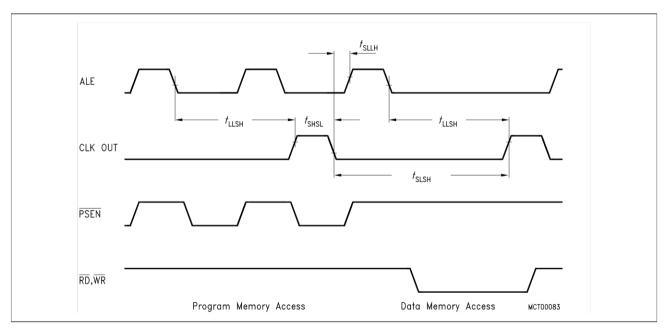

| PSEN        | 22                 | 49       | 0     | The Program Store Enable output is a control signal that enables the external program memory to the bus during external fetch operations. It is activated every six oscillator periods except during external data memory accesses. The signal remains high during internal program execution.                                                                                                                                                                                                                         |  |

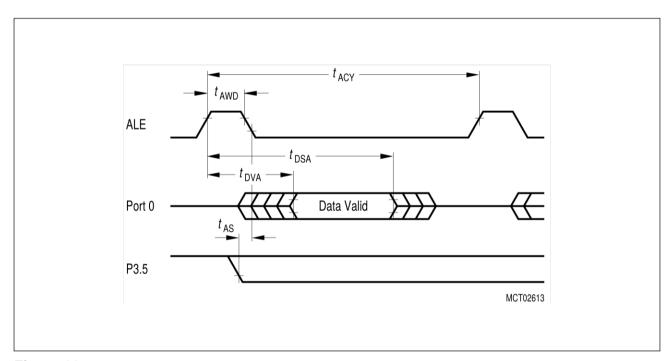

| ALE         | 23                 | 50       | 0     | The Address Latch enable output is used for latching the address into external memory during normal operation. It is activated every six oscillator periods except during an external data memory access.                                                                                                                                                                                                                                                                                                              |  |

| ĒΑ          | 24                 | 51       | I     | External Access Enable When held high, the C517A executes instructions from the internal ROM as long as the PC is less than 8000 <sub>H</sub> . When held low, the C517A fetches all instructions from external program memory. For the C517A-L this pin must be tied low. For the C517A-4R, if the device is protected (see section 4.6 in the User Manual) then this pin is only latched during reset.                                                                                                               |  |

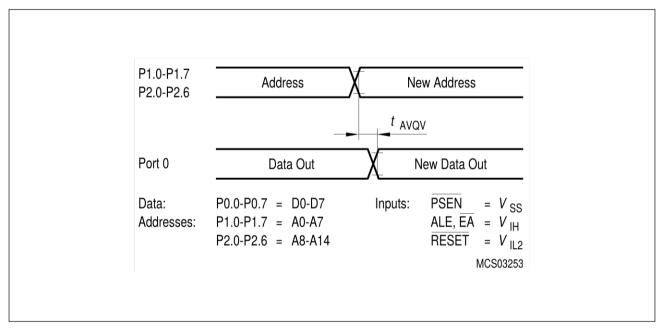

| P0.0 - P0.7 | 26, 27,<br>30 - 35 | 52 - 59  | I/O   | Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1's written to them float, and in that state can be used as high- impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application it uses strong internal pullup resistors when issuing 1's. Port 0 also outputs the code bytes during program verification in the C517A- 4R. External pullup resistors are required during program verification. |  |

<sup>\*)</sup> I = Input O = Output

Table 1

Pin Definitions and Functions (cont'd)

| Symbol      | Pin Number |          | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------|------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | P-MQFP-100 | P-LCC-84 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| HWPD        | 36         | 60       | I     | Hardware Power Down A low level on this pin for the duration of one machine cycle while the oscillator is running resets the C517A. A low level for a longer period will force the part into hardware power down mode with the pins floating. There is no internal pullup resistor connected to this pin.                                                                                                                                                                                                                                                                                                |  |

| P5.0 - P5.7 | 44 - 37    | 68 - 61  | I/O   | is a quasi-bidirectional I/O port with internal pull-up resistors. Port 5 pins that have 1 s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, port 5 pins being externally pulled low will source current (I <sub>IL</sub> , in the DC characteristics) because of the internal pull-up resistors. This port also serves the alternate function "Concurrent Compare" and "Set/Reset Compare". The secondary functions are assigned to the port 5 pins as follows: CCM0 to CCM7 P5.0 to P5.7: concurrent compare or Set/Reset lines |  |

| OWE         | 45         | 69       | I     | Oscillator Watchdog Enable A high level on this pin enables the oscillator watchdog. When left unconnected this pin is pulled high by a weak internal pull-up resisitor. The logic level at OWE should not be changed during normal operation. When held at low level the oscillator watchdog function is turned off. During hardware power down the pullup resistor is switched off.                                                                                                                                                                                                                    |  |

<sup>\*)</sup> I = Input O = Output

Table 1 Pin Definitions and Functions (cont'd)

| Symbol      | Pin Number                            |                     | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------|---------------------------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | P-MQFP-100                            | P-LCC-84            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| P6.0 - P6.7 | 46 - 50,<br>54 - 56<br>46<br>47<br>48 | 70 - 77<br>71<br>72 | I/O   | Port 6  is a quasi-bidirectional I/O port with internal pull-up resistors. Port 6 pins that have 1 s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, port 6 pins being externally pulled low will source current ( <i>I</i> IL, in the DC characteristics) because of the internal pull-up resistors. Port 6 also contains the external A/D converter start control pin and the transmit and receive pins for the serial interface 1. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate. The secondary functions are assigned to the pins of port 6, as follows:  P6.0 ADST external A/D converter start pin  P6.1 RxD1 receiver data input of serial interface 1  P6.2 TxD1 transmitter data input of serial interface 1 |  |  |

| P8.0 - P8.3 | 57 - 60                               | 78 - 81             | 1     | Port 8 is a 4-bit unidirectional input port. Port pins can be used for digital input, if voltage levels meet the specified input high/low voltages, and for the higher 4-bit of the multiplexed analog inputs of the A/D converter, simultaneously.  P8.0 - P8.3 AIN8 - AIN11 analog input 8 - 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RO          | 61                                    | 82                  | 0     | Reset Output This pin outputs the internally synchronized reset request signal. This signal may be generated by an external hardware reset, a watchdog timer reset or an oscillator watchdog reset. The RO output signal is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

<sup>\*)</sup> I = Input O = Output

Table 1

Pin Definitions and Functions (cont'd)

| Symbol      | Pin Number          |                 | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------|---------------------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | P-MQFP-100          | P-LCC-84        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| P4.0 - P4.7 | 64 - 66,<br>68 - 72 | 1 - 3,<br>5 - 9 | I/O   | is an 8-bit quasi-bidirectional I/O port with internal pull-up resistors. Port 4 pins that have 1's written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, por 4 pins being externally pulled low will source current ( <i>I</i> <sub>IL</sub> , in the DC characteristics) because of the internal pull-up resistors. Port 4 also serves as alternate compare functions. The output latch corresponding to a secondary function must be programme to a one (1) for that function to operate. The secondary functions are assigned to the pins of port 4 as follows:  P4.0 - P4.7 CM0 - CM7 Compare channel 0 - 7 |  |  |

| PE/SWD      | 67                  | 4               |       | Power saving mode enable / Start watchdog timer A low level at this pin allows the software to enter the power saving modes (idle mode slow down mode, and power down mode) In case the low level is also seen during reset, the watchdog timer function is off or default.  Usage of the software controlled power saving modes is blocked, when this pin is held at high level. A high level during rese performs an automatic start of the watchdo timer immediately after reset.  When left unconnected this pin is pulled high by a weak internal pull-up resistor.  During hardware power down the pullup resisitor is switched off.                                        |  |  |

<sup>\*)</sup> I = Input O = Output

Table 1 Pin Definitions and Functions (cont'd)

| Symbol      | Pin N      | umber    | I/O*) | Function                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------|------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | P-MQFP-100 | P-LCC-84 |       |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| P3.0 - P3.7 | 90 - 97    | 21 - 28  | I/O   | internal pullup have 1's writter the internal pull can be used as being externall current ( <i>I</i> <sub>IL</sub> , in because of the 3 also contains port and externare used by valatch correspormust be prografunction to ope | si-bidirectional I/O port with resistors. Port 3 pins that n to them are pulled high by lup resistors, and in that states inputs. As inputs, port 3 pindly pulled low will source the DC characteristics) internal pullup resistors. Post the interrupt, timer, serial nal memory strobe pins that arious options. The output anding to a secondary function ammed to a one (1) for that erate. The secondary assigned to the pins of port 3 |  |

|             | 90         | 21       |       | P3.0 / RxD0                                                                                                                                                                                                                      | Receiver data input (asynch.) or data input/output (synch.)of serial interface 0                                                                                                                                                                                                                                                                                                                                                             |  |

|             | 91         | 22       |       | P3.1 / TxD0                                                                                                                                                                                                                      | Transmitter data output (asynch.) or clock output (synch.) of serial interface 0                                                                                                                                                                                                                                                                                                                                                             |  |

|             | 92         | 23       |       | P3.2 / ĪNT0                                                                                                                                                                                                                      | External interrupt 0 input / timer 0 gate control input                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 93         | 24       |       | P3.3 / ĪNT1                                                                                                                                                                                                                      | External interrupt 1 input / timer 1 gate control input                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 94         | 25       |       | P3.4 / T0                                                                                                                                                                                                                        | Timer 0 counter input                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|             | 95         | 26       |       | P3.5 / T1                                                                                                                                                                                                                        | Timer 1 counter input                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|             | 96         | 27       |       | P3.6 / WR                                                                                                                                                                                                                        | WR control output; latches the data byte from port 0 into the external data memory                                                                                                                                                                                                                                                                                                                                                           |  |

|             | 97         | 28       |       | P3.7 / RD                                                                                                                                                                                                                        | RD control output; enables the external data memory                                                                                                                                                                                                                                                                                                                                                                                          |  |

<sup>\*)</sup> I = Input O = Output

Table 1

Pin Definitions and Functions (cont'd)

| Symbol            | Pin N                                                  | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------|--------------------------------------------------------|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | P-MQFP-100                                             | P-LCC-84 |       |                                                                                                                                                                                                                                                                                                |  |  |  |

| RESET             | 73                                                     | 10       | I     | RESET A low level on this pin for the duration of two machine cycles while the oscillator is running resets the C517A. A small internal pullup resistor permits power-on reset using only a capacitor connected to V <sub>SS</sub> .                                                           |  |  |  |

| V <sub>AREF</sub> | 78                                                     | 11       | -     | Reference voltage for the A/D converter                                                                                                                                                                                                                                                        |  |  |  |

| $V_{AGND}$        | 79                                                     | 12       | -     | Reference ground for the A/D converter                                                                                                                                                                                                                                                         |  |  |  |

| P7.0 - P7.7       | 87 - 80                                                | 20-13    | I     | Port 7 is an 8-bit unidirectional input port. Port pins can be used for digital input, if voltage levels meet the specified input high/low voltages, and for the lower 8-bit of the multiplexed analog inputs of the A/D converter, simultaneously.  P7.0 - P7.7 AINO - AIN7 analog input0 - 7 |  |  |  |

| N.C.              | 2 - 5, 25,<br>28, 29,<br>51 - 53,<br>74 - 77<br>88, 89 | _        | _     | Not connected These pins of the P-MQFP-100 package must not be connected.                                                                                                                                                                                                                      |  |  |  |

<sup>\*)</sup> I = Input O = Output

Figure 5

Block Diagram of the C517A

Reset Value: 00H

## **CPU**

The C517A is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and 15% three-byte instructions. With a 12 MHz crystal, 58% of the instructions are executed in 1 $\mu$ s (24 MHz : 500 ns).

## Special Function Register PSW (Address D0<sub>H</sub>)

| Bit No.  | MSB | MSB |       |     |     |                 |    |   |     |

|----------|-----|-----|-------|-----|-----|-----------------|----|---|-----|

|          |     |     | • • • |     |     | D2 <sub>H</sub> |    |   | _   |

| $D0_{H}$ | CY  | AC  | F0    | RS1 | RS0 | OV              | F1 | Р | PSW |

| Bit        | Function                   | Function                                                                                         |                                                                |  |  |  |  |

|------------|----------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| CY         | Carry Flag<br>Used by ar   | Carry Flag Used by arithmetic instruction.                                                       |                                                                |  |  |  |  |

| AC         | Auxiliary C<br>Used by in: | -                                                                                                | which execute BCD operations.                                  |  |  |  |  |

| F0         | General Pu                 | ırpose Fla                                                                                       | g                                                              |  |  |  |  |

| RS1<br>RS0 |                            | Register Bank select control bits  These bits are used to select one of the four register banks. |                                                                |  |  |  |  |

|            | RS1                        | RS0                                                                                              | Function                                                       |  |  |  |  |

|            | 0                          | 0                                                                                                | Bank 0 selected, data address 00 <sub>H</sub> -07 <sub>H</sub> |  |  |  |  |

|            | 0                          | 1                                                                                                | Bank 1 selected, data address 08 <sub>H</sub> -0F <sub>H</sub> |  |  |  |  |

|            | 1                          | 0                                                                                                | Bank 2 selected, data address 10 <sub>H</sub> -17 <sub>H</sub> |  |  |  |  |

|            | 1                          | 1                                                                                                | Bank 3 selected, data address 18 <sub>H</sub> -1F <sub>H</sub> |  |  |  |  |

| OV         |                            | Overflow Flag Used by arithmetic instruction.                                                    |                                                                |  |  |  |  |

| F1         | General Pu                 | General Purpose Flag                                                                             |                                                                |  |  |  |  |

| P          |                            |                                                                                                  |                                                                |  |  |  |  |

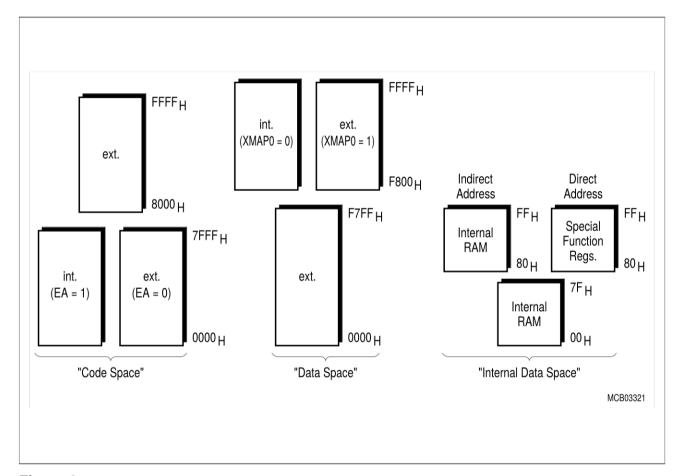

#### **Memory Organization**

The C517A CPU manipulates operands in the following five address spaces:

- up to 64 Kbyte of program memory (32K on-chip program memory for C517A-4R)

- up to 64 Kbyte of external data memory

- 256 bytes of internal data memory

- 2K bytes of internal XRAM data memory

- a 128 byte special function register area

Figure 6 illustrates the memory address spaces of the C517A.

Figure 6 C517A Memory Map

## **Reset and System Clock**

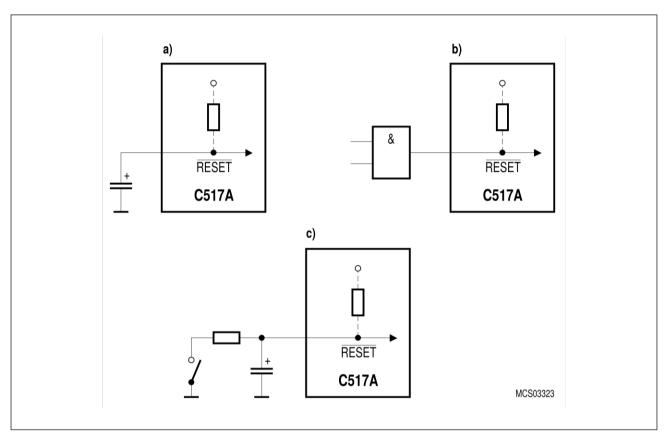

The reset input is an active low input at pin  $\overline{\text{RESET}}$ . Since the reset is synchronized internally, the  $\overline{\text{RESET}}$  pin must be held low for at least two machine cycles (24 oscillator periods) while the oscillator is running. A pullup resistor is internally connected to  $V_{\text{DD}}$  to allow a power-up reset with an external capacitor only. An automatic reset can be obtained when  $V_{\text{DD}}$  is applied by connecting the  $\overline{\text{RESET}}$  pin to  $V_{\text{SS}}$  via a capacitor. **Figure 7** shows the possible reset circuitries.

Figure 7

Reset Circuitries

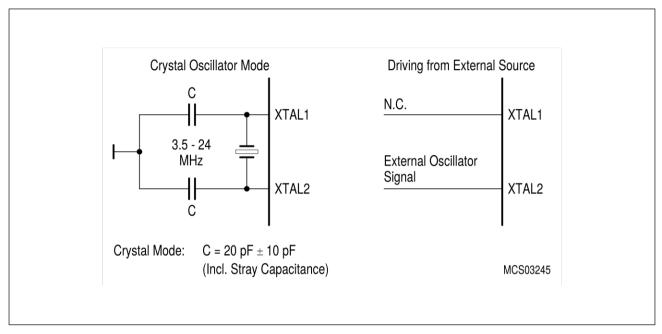

Figure 8 shows the recommended oscillator circiutries for crystal and external clock operation.

Figure 8

Recommended Oscillator Circuitries

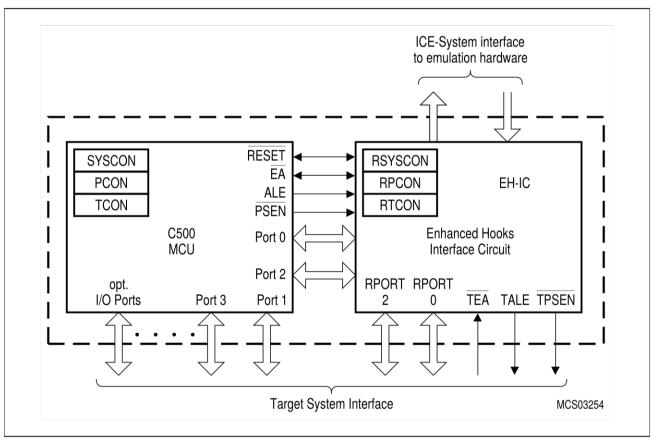

#### **Enhanced Hooks Emulation Concept**

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative way to control the execution of C500 MCUs and to gain extensive information on the internal operation of the controllers. Emulation of on-chip ROM based programs is possible, too.

Each production chip has built-in logic for the supprt of the Enhanced Hooks Emulation Concept. Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation and production chips are identical.

The Enhanced Hooks Technology<sup>TM 1)</sup>, which requires embedded logic in the C500 allows the C500 together with an EH-IC to function similar to a bond-out chip. This simplifies the design and reduces costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate all operating modes of the different versions of the C500 microcontrollers. This includes emulation of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in single step mode and to read the SFRs after a break.

Figure 9

Basic C500 MCU Enhanced Hooks Concept Configuration

Port 0, port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks Emulation Concept to control the operation of the device during emulation and to transfer informations about the programm execution and data transfer between the external emulation hardware (ICE-system) and the C500 MCU.

<sup>1 &</sup>quot;Enhanced Hooks Technology" is a trademark and patent of Metalink Corporation licensed to Siemens.

## **Special Function Registers**

The registers, except the program counter and the four general purpose register banks, reside in the special function register area.

The 94 special function registers (SFRs) in the standard and mapped SFR area include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. All SFRs with addresses where address bits 0-2 are 0 (e

.g.  $80_H$ ,  $88_H$ ,  $90_H$ ,  $98_H$ , ...,  $F8_H$ ,  $FF_H$ ) are bitaddressable. The SFRs of the C517A are listed in **table 2** and **table 3**. In **table 2** they are organized in groups which refer to the functional blocks of the C517A. **Table 3** illustrates the contents of the SFRs in numeric order of their addresses.

Table 2 Special Function Registers - Functional Blocks

| Block                | Symbol                                                                                                                                                                      | Name                                                                                                                                                                                                                                                                                                                                           | Address                                                                                                                     | Contents after<br>Reset                                                                                                                                                                                                 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                  | ACC<br>B<br>DPH<br>DPL<br>DPSEL<br>PSW<br>SP                                                                                                                                | Accumulator B-Register Data Pointer, High Byte Data Pointer, Low Byte Data Pointer Select Register Program Status Word Register Stack Pointer                                                                                                                                                                                                  | E0H <sup>1)</sup> F0H <sup>1)</sup> 83H 82H 92H D0H <sup>1)</sup>                                                           | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>XXXX X000 <sub>B</sub> 3)<br>00 <sub>H</sub><br>07 <sub>H</sub>                                                                             |

| A/D-<br>Converter    | ADCON0 <sup>2)</sup><br>ADCON1<br>ADDATH<br>ADDATL                                                                                                                          | A/D Converter Control Register 0 A/D Converter Control Register 1 A/D Converter Data Register, High Byte A/D Converter Data Register, Low Byte                                                                                                                                                                                                 | D8 <sub>H</sub> 1)<br>DC <sub>H</sub><br>D9 <sub>H</sub><br>DA <sub>H</sub>                                                 | 00H<br>00XX XXXXB <sup>3</sup>                                                                                                                                                                                          |

| Interrupt<br>System  | IEN0 <sup>2)</sup> IEN1 <sup>2)</sup> IEN2 IP0 <sup>2)</sup> IP1 IRCON0 <sup>2)</sup> IRCON1 TCON <sup>2)</sup> T2CON <sup>2)</sup> S0CON <sup>2)</sup> CTCON <sup>2)</sup> | Interrupt Enable Register 0 Interrupt Enable Register 1 Interrupt Enable Register 2 Interrupt Priority Register 0 Interrupt Priority Register 1 Interrupt Request Control Register 0 Interrupt Request Control Register 1 Timer 0/1 Control Register Timer 2 Control Register Serial Channel 0 Control Register Compare Timer Control Register | A8H <sup>1)</sup> B8H <sup>1)</sup> 9AH A9H B9H C0H <sup>1)</sup> D1H 88H <sup>1)</sup> C8H <sup>1)</sup> 98H <sup>1)</sup> | 00H<br>00H<br>XX00 00X0B <sup>3)</sup><br>00H<br>XX00 0000B <sup>3)</sup><br>00H<br>00H<br>00H<br>00H<br>00H<br>00H                                                                                                     |

| MUL/DIV<br>Unit      | ARCON<br>MD0<br>MD1<br>MD2<br>MD3<br>MD4<br>MD5                                                                                                                             | Arithmetic Control Register Multiplication/Division Register 0 Multiplication/Division Register 1 Multiplication/Division Register 2 Multiplication/Division Register 3 Multiplication/Division Register 4 Multiplication/Division Register 5                                                                                                  | EFH<br>E9H<br>EAH<br>EBH<br>ECH<br>EDH<br>EEH                                                                               | 0XXXXXXX <sub>B</sub> <sup>3)</sup> XX <sub>H</sub> <sup>3)</sup> |

| Timer 0 /<br>Timer 1 | TCON <sup>2)</sup> TH0 TH1 TL0 TL1 TMOD                                                                                                                                     | Timer 0/1 Control Register Timer 0, High Byte Timer 1, High Byte Timer 0, Low Byte Timer 1, Low Byte Timer Mode Register                                                                                                                                                                                                                       | 88 <sub>H</sub> 1)<br>8C <sub>H</sub><br>8D <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>89 <sub>H</sub>           | 00H<br>00H<br>00H<br>00H<br>00H                                                                                                                                                                                         |

<sup>1)</sup> Bit-addressable special function registers

<sup>2)</sup> This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

<sup>3) &</sup>quot;X" means that the value is undefined and the location is reserved

Table 2

Special Function Registers - Functional Blocks (cont'd)

| Block     | Symbol             | Name                                                                   | Address          | Contents after Reset                  |

|-----------|--------------------|------------------------------------------------------------------------|------------------|---------------------------------------|

| Compare/  | CCEN               | Compare/Capture Enable Register                                        | C1 <sub>H</sub>  | 00 <sub>H</sub>                       |

| Capture   | CC4EN              | Compare/Capture 4 Enable Register                                      | C9H              | 00H                                   |

| Unit      | CCH1               | Compare/Capture Register 1, High Byte                                  | C3H              | 00H                                   |

| (CCU)     | CCH2               | Compare/Capture Register 2, High Byte                                  | C5 <sub>H</sub>  | 00H                                   |

| Timer 2   | CCH3               | Compare/Capture Register 3, High Byte                                  | C7 <sub>H</sub>  | 00H                                   |

| 1111101 = | CCH4               | Compare/Capture Register 4, High Byte                                  | CFH              | 00H                                   |

|           | CCL1               | Compare/Capture Register 1, Low Byte                                   | C2 <sub>H</sub>  | 00H                                   |

|           | CCL2               | Compare/Capture Register 2, Low Byte                                   | C4 <sub>H</sub>  | 00H                                   |

|           | CCL3               | Compare/Capture Register 3, Low Byte                                   | Cerr             | 00H                                   |

|           | CCL4               | Compare/Capture Register 4, Low Byte                                   | C6H              | 00H                                   |

|           | CMEN               |                                                                        | CEH              | 00H                                   |

|           |                    | Compare Enable Register                                                | F6H              | 00H                                   |

|           | CMH0               | Compare Register 0, High Byte                                          | D3H              | 00H                                   |

|           | CMH1               | Compare Register 1, High Byte                                          | D5H              | 00H                                   |

|           | CMH2               | Compare Register 2, High Byte                                          | D7H              | 00H                                   |

|           | CMH3               | Compare Register 3, High Byte                                          | E3 <sub>H</sub>  | 00H                                   |

|           | CMH4               | Compare Register 4, High Byte                                          | E <sub>5</sub> H | 00H                                   |

|           | CMH5               | Compare Register 5, High Byte                                          | E7 <sub>H</sub>  | 00 <sub>H</sub>                       |

|           | CMH6               | Compare Register 6, High Byte                                          | F3 <sub>H</sub>  | 00H                                   |

|           | CMH7               | Compare Register 7, High Byte                                          | F5 <sub>H</sub>  | 00H                                   |

|           | CML0               | Compare Register 0, Low Byte                                           | D2H              | 00 <sub>H</sub>                       |

|           | CML1               | Compare Register 1, Low Byte                                           | D4 <sub>H</sub>  | 00 <sub>H</sub>                       |

|           | CML2               | Compare Register 2, Low Byte                                           | D6H              | ∣00 <sub>H</sub>                      |

|           | CML3               | Compare Register 3, Low Byte                                           | E2 <sub>H</sub>  | ∣ 00 <sub>H</sub>                     |

|           | CML4               | Compare Register 4, Low Byte                                           | E4H              | 00H                                   |

|           | CML5               | Compare Register 5, Low Byte                                           | E6H              | 00 <sub>H</sub>                       |

|           | CML6               | Compare Register 6, Low Byte                                           | F2H              | 00H                                   |

|           | CML7               | Compare Register 7, Low Byte                                           | F4H              | 00H                                   |

|           | CMSEL              | Compare Input Select                                                   | F7H              | 00H                                   |

|           | CRCH               | Comp./Rel./Capt. Register High Byte                                    | СВН              | 00H                                   |

|           | CRCL               | Comp./Rel./Capt. Register Low Byte                                     | CAH              | 00H                                   |

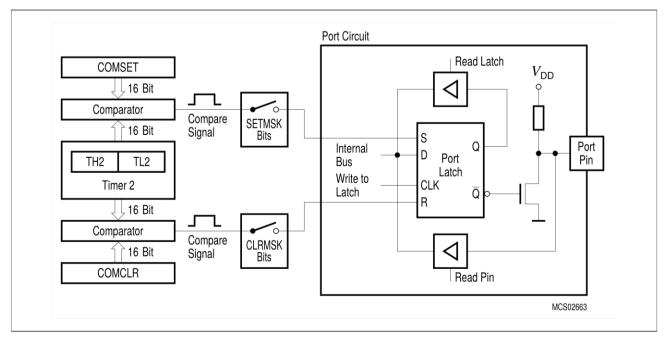

|           | COMSETL            | Compare Set Register Low Byte                                          | A1H              | 00H                                   |

|           | COMSETH            | Compare Set Register, High Byte                                        | A2 <sub>H</sub>  | 00H                                   |

|           | COMCLRL            | Compare Clear Register, Low Byte                                       | A3 <sub>H</sub>  | 00H                                   |

|           | COMCLRH            | Compare Clear Register, High Byte                                      | A4 <sub>H</sub>  | 00H                                   |

|           | SETMSK             | Compare Set Mask Register                                              | A5 <sub>H</sub>  | 00H                                   |

|           | CLRMSK             | Compare Clear Mask Register                                            | A6 <sub>H</sub>  | 00H                                   |

|           | CTCON 2)           | Compare Timer Control Register                                         |                  | 0X00 0000 <sub>B</sub> <sup>3</sup> ) |

|           | CTRELH             | Compare Timer Control Register  Compare Timer Rel. Register, High Byte | DF <sub>H</sub>  | 00H                                   |

|           | CTRELL             | Compare Timer Rel. Register, Low Byte                                  | DEH              | 00H                                   |

|           | TH2                | Timer 2, High Byte                                                     | CDH              | 00H                                   |

|           | TL2                | Timer 2, High Byte Timer 2, Low Byte                                   | CCH              | 00H                                   |

|           | T2CON 2)           |                                                                        | CCH<br>C8::1)    | 00H                                   |

|           | IRCON <sup>2</sup> | Timer 2 Control Register Interrupt Request Control Register 0          | C8H 1)           | 00H                                   |

|           | INCOMU 2           | interrupt nequest Control negister 0                                   | C0H 1)           | 00H                                   |

<sup>1)</sup> Bit-addressable special function registers

<sup>2)</sup> This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

<sup>3) &</sup>quot;X" means that the value is undefined and the location is reserved

Table 2 Special Function Registers - Functional Blocks (cont'd)

| Block              | Symbol                                                                                      | Name                                                                                                                                                                                                                                                                                                                                                      | Address                                                                                                                                                                                   | Contents after<br>Reset                                                                                                                                                                                                                                                                    |

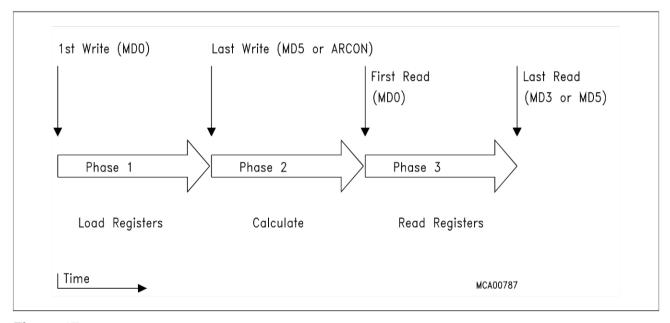

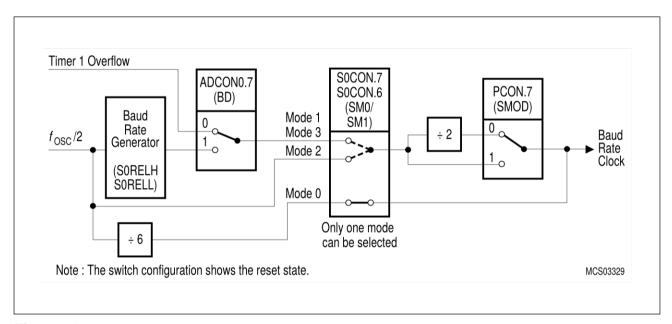

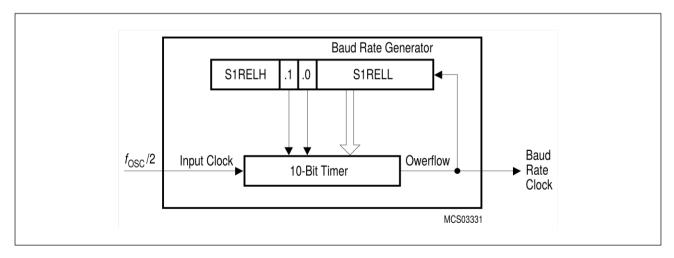

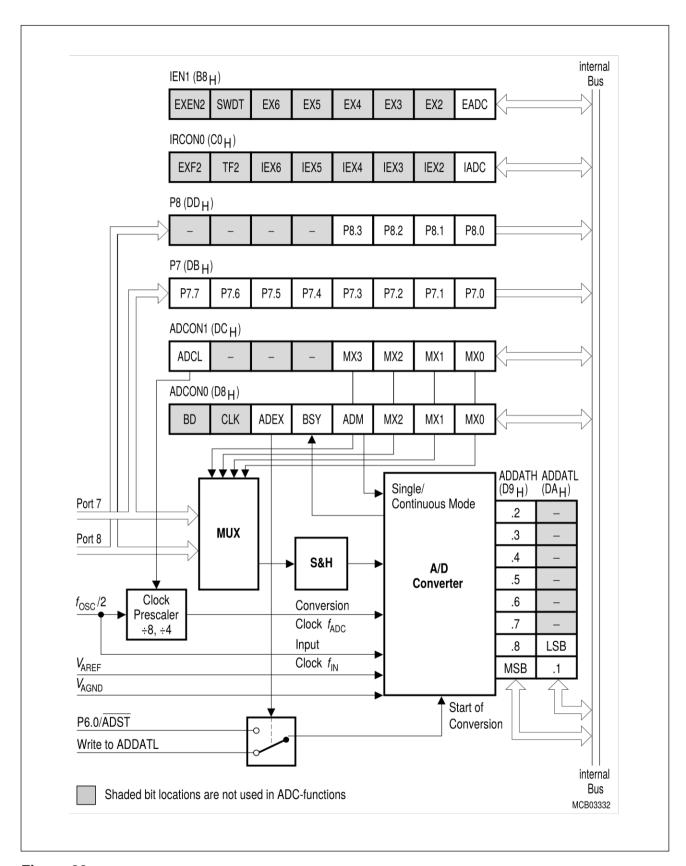

|--------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|