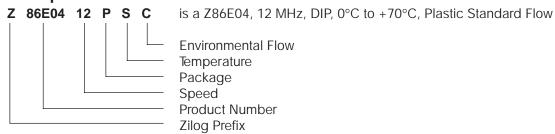

# **Z86E04/E08**CMOS Z8 OTP MICROCONTROLLERS

# **PRODUCT DEVICES**

| Part            | Oscillator | Operating       | Operating   | ROM  |             |

|-----------------|------------|-----------------|-------------|------|-------------|

| Number          | Type       | V <sub>cc</sub> | Temperature | (KB) | Package     |

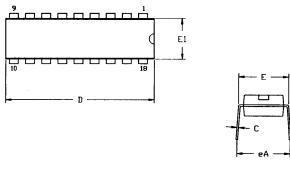

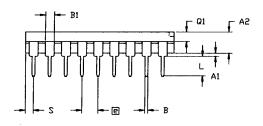

| Z86E0412PEC     | Crystal    | 4.5V-5.5V       | -40°C/105°C | 1    | 18-Pin DIP  |

| Z86E0412PSC1866 | Crystal    | 4.5V-5.5V       | 0°C/70°C    | 1    | 18-Pin DIP  |

| Z86E0412PSC1903 | RC         | 4.5V-5.5V       | 0°C/70°C    | 1    | 18-Pin DIP  |

| Z86E0412PEC1903 | RC         | 4.5V-5.5V       | -40°C/105°C | 1    | 18-Pin DIP  |

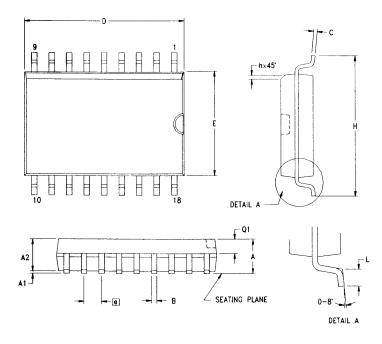

| Z86E0412SEC     | Crystal    | 4.5V-5.5V       | -40°C/105°C | 1    | 18-Pin SOIC |

| Z86E0412SSC1866 | Crystal    | 4.5V-5.5V       | 0°C/70°C    | 1    | 18-Pin SOIC |

| Z86E0412SSC1903 | RC         | 4.5V-5.5V       | 0°C/70°C    | 1    | 18-Pin SOIC |

| Z86E0412SEC1903 | RC         | 4.5V-5.5V       | -40°C/105°C | 1    | 18-Pin SOIC |

| Z86E0812PEC     | Crystal    | 4.5V-5.5V       | -40°C/105°C | 2    | 18-Pin DIP  |

| Z86E0812PSC1866 | Crystal    | 4.5V-5.5V       | 0°C/70°C    | 2    | 18-Pin DIP  |

| Z86E0812PSC1903 | RC         | 4.5V-5.5V       | 0°C/70°C    | 2    | 18-Pin DIP  |

| Z86E0812PEC1903 | RC         | 4.5V-5.5V       | -40°C/105°C | 2    | 18-Pin DIP  |

| Z86E0812SEC     | Crystal    | 4.5V-5.5V       | -40°C/105°C | 2    | 18-Pin SOIC |

| Z86E0812SSC1866 | Crystal    | 4.5V-5.5V       | 0°C/70°C    | 2    | 18-Pin SOIC |

| Z86E0812SSC1903 | RC         | 4.5V-5.5V       | 0°C/70°C    | 2    | 18-Pin SOIC |

| Z86E0812SEC1903 | RC         | 4.5V-5.5V       | -40°C/105°C | 2    | 18-Pin SOIC |

Several key product features of the extensive family of Zilog Z86E04/E08 CMOS OTP microcontrollers are presented in the above table. This table enables the user to identify which of the E04/E08 product variants most closely match the user's application requirements.

# **FEATURES**

- 14 Input/Output Lines

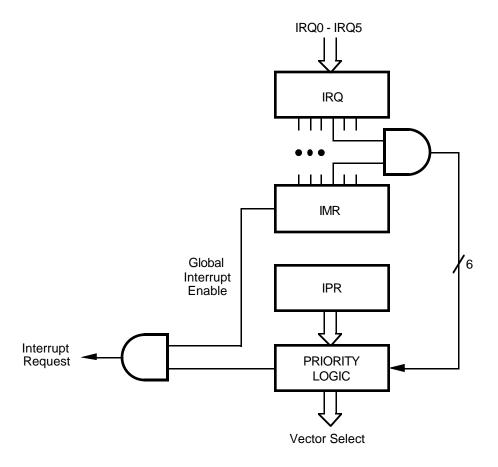

- Six Vectored, Prioritized Interrupts

(3 falling edge, 1 rising edge, 2 timers)

- Two Analog Comparators

- Program Options:

- Low Noise

- ROM Protect

- Auto Latch

- Watch-Dog Timer (WDT)

- EPROM/Test Mode Disable

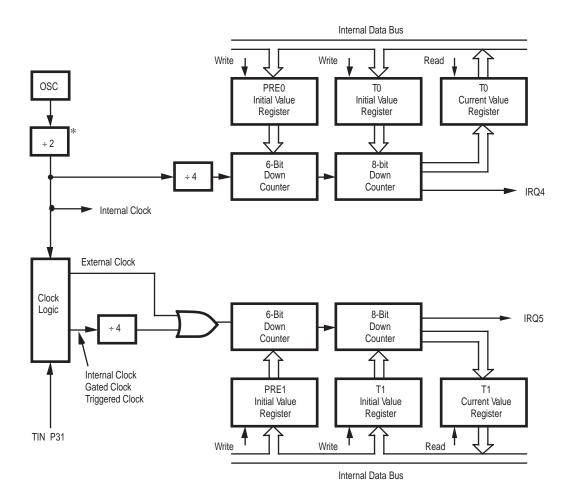

- Two Programmable 8-Bit Counter/Timers, Each with 6-Bit Programmable Prescaler

- WDT/ Power-On Reset (POR)

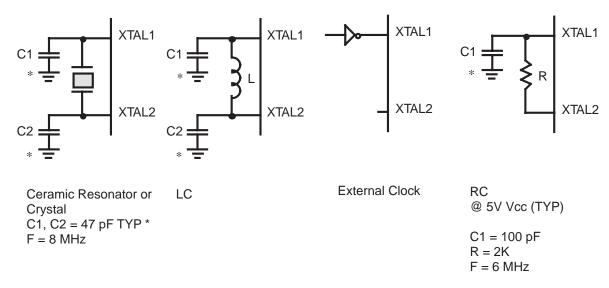

- On-Chip Oscillator that Accepts XTAL, Ceramic Resonance, LC, RC, or External Clock

- Clock-Free WDT Reset

- Low-Power Consumption (50 mw typical)

- Fast Instruction Pointer (1µs @ 12 MHz)

- RAM Bytes (125)

#### **GENERAL DESCRIPTION**

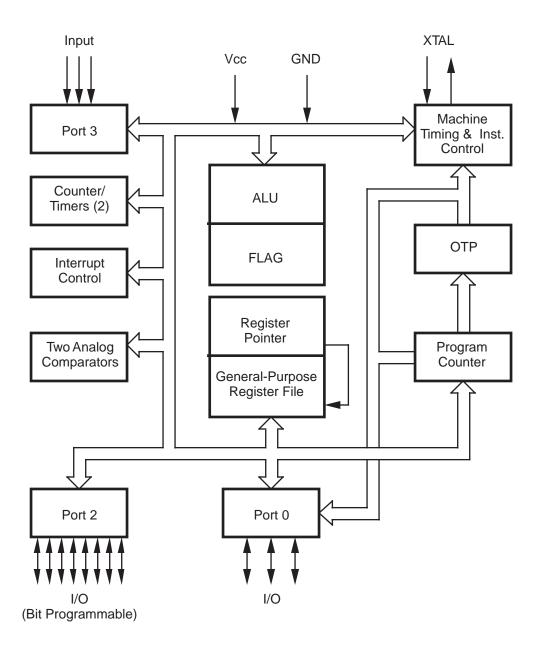

Zilog's Z86E04/E08 Microcontrollers (MCU) are One-Time Programmable (OTP) members of Zilog's single-chip Z8<sup>®</sup> MCU family that allow easy software development, debug, prototyping, and small production runs not economically desirable with masked ROM versions.

For applications demanding powerful I/O capabilities, the Z86E04/E08's dedicated input and output lines are grouped into three ports, and are configurable under software control to provide timing, status signals, or parallel I/O.

Two on-chip counter/timers, with a large number of user selectable modes, offload the system of administering real-time tasks such as counting/timing and I/O data communications.

**Note:** All Signals with an overline, " $\overline{}$ ", are active Low, for example:  $\overline{B/W}$  (WORD is active Low);  $\overline{B/W}$  (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | $V_{SS}$        |

Figure 1. Functional Block Diagram

# **GENERAL DESCRIPTION** (Continued)

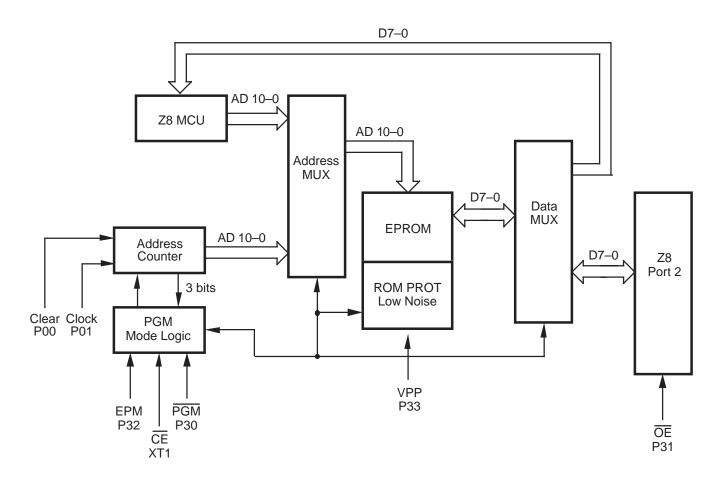

Figure 2. EPROM Programming Mode Block Diagram

#### PIN DESCRIPTION

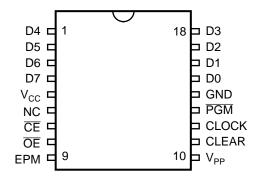

Figure 3. 18-Pin EPROM Mode Configuration

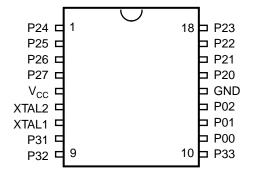

Figure 4. 18-Pin DIP/SOIC Mode Configuration

Table 1. 18-Pin DIP Pin Identification

| <b>EPROM</b> | Programmi       | ng Mode         |           |

|--------------|-----------------|-----------------|-----------|

| Pin#         | Symbol          | Function        | Direction |

| 1–4          | D4-D7           | Data 4, 5, 6, 7 | In/Output |

| 5            | V <sub>CC</sub> | Power Supply    |           |

| 6            | NC              | No Connection   |           |

| 7            | CE              | Chip Enable     | Input     |

| 8            | ŌĒ              | Output Enable   | Input     |

| 9            | EPM             | EPROM Prog Mode | Input     |

| 10           | $V_{PP}$        | Prog Voltage    | Input     |

| 11           | Clear           | Clear Clock     | Input     |

| 12           | Clock           | Address         | Input     |

| 13           | PGM             | Prog Mode       | Input     |

| 14           | GND             | Ground          |           |

| 15–18        | D0-D3           | Data 0,1, 2, 3  | In/Output |

Table 2. 18-Pin DIP/SOIC Pin Identification

| Standard Mode |                 |                      |           |  |  |  |  |  |

|---------------|-----------------|----------------------|-----------|--|--|--|--|--|

| Pin#          | Symbol          | Function             | Direction |  |  |  |  |  |

| 1–4           | P24-P27         | Port 2, Pins 4,5,6,7 | In/Output |  |  |  |  |  |

| 5             | V <sub>CC</sub> | Power Supply         |           |  |  |  |  |  |

| 6             | XTAL2           | Crystal Osc. Clock   | Output    |  |  |  |  |  |

| 7             | XTAL1           | Crystal Osc. Clock   | Input     |  |  |  |  |  |

| 8             | P31             | Port 3, Pin 1, AN1   | Input     |  |  |  |  |  |

| 9             | P32             | Port 3, Pin 2, AN2   | Input     |  |  |  |  |  |

| 10            | P33             | Port 3, Pin 3, REF   | Input     |  |  |  |  |  |

| 11–13         | P00-P02         | Port 0, Pins 0,1,2   | In/Output |  |  |  |  |  |

| 14            | GND             | Ground               |           |  |  |  |  |  |

| 15–18         | P20-P23         | Port 2, Pins 0,1,2,3 | In/Output |  |  |  |  |  |

|               |                 |                      |           |  |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability. Total power

dissipation should not exceed 462 mW for the package. Power dissipation is calculated as follows:

Total Power Dissipation =

$$V_{DD} \times [I_{DD} - (sum of I_{OH})]$$

+ sum of  $[(V_{DD} - V_{OH}) \times I_{OH}]$

+ sum of  $(V_{0I} \times I_{OI})$

| Parameter                                                      | Min  | Max                | Units | Note |

|----------------------------------------------------------------|------|--------------------|-------|------|

| Ambient Temperature under Bias                                 | -40  | +105               | С     |      |

| Storage Temperature                                            | -65  | +150               | С     |      |

| Voltage on any Pin with Respect to V <sub>SS</sub>             | -0.7 | +12                | V     | 1    |

| Voltage on V <sub>DD</sub> Pin with Respect to V <sub>SS</sub> | -0.3 | +7                 | V     |      |

| Voltage on Pins 7, 8, 9, 10 with Respect to V <sub>SS</sub>    | -0.6 | V <sub>DD</sub> +1 | V     | 2    |

| Total Power Dissipation                                        |      | 1.65               | W     |      |

| Maximum Allowable Current out of V <sub>SS</sub>               |      | 300                | mA    |      |

| Maximum Allowable Current into V <sub>DD</sub>                 |      | 220                | mA    |      |

| Maximum Allowable Current into an Input Pin                    | -600 | +600               | μΑ    | 3    |

| Maximum Allowable Current into an Open-Drain Pin               | -600 | +600               | μΑ    | 4    |

| Maximum Allowable Output Current Sinked by Any I/O Pin         |      | 25                 | mA    |      |

| Maximum Allowable Output Current Sourced by Any I/O Pin        |      | 25                 | mA    |      |

| Total Maximum Output Current Sinked by a Port                  |      | 60                 | mA    |      |

| Total Maximum Output Current Sourced by a Port                 |      | 45                 | mA    |      |

#### Notes:

- 1. This applies to all pins except where otherwise noted. Maximum current into pin must be  $\pm\,600~\mu\text{A}$ .

- 2. There is no input protection diode from pin to  $V_{DD}$  (not applicable to EPROM Mode).

- 3. This excludes Pin 6 and Pin 7.

- 4. Device pin is not at an output Low state.

# STANDARD TEST CONDITIONS

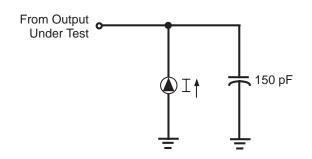

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 5).

Figure 5. Test Load Diagram

# **CAPACITANCE**

$T_A = 25$ °C,  $V_{CC} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 10 pF |

| Output capacitance | 0   | 20 pF |

| I/O capacitance    | 0   | 25 pF |

Standard Temperature

|                               |                                                  |                     | $T_A = 0^{\circ}C$   | to +70°C             | Typical |       |                                        |       |

|-------------------------------|--------------------------------------------------|---------------------|----------------------|----------------------|---------|-------|----------------------------------------|-------|

| Sym                           | Parameter                                        | V <sub>CC</sub> [4] | Min                  | Max                  | @ 25°C  | Units | Conditions                             | Notes |

| $\overline{V_{\text{INMAX}}}$ | Max Input Voltage                                | 4.5V                |                      | 12                   |         | V     | I <sub>In</sub> <250 μA                | 1     |

|                               | -                                                | 5.5V                |                      | 12                   |         | V     | I <sub>In</sub> <250 μA                | 1     |

| V <sub>CH</sub>               | Clock Input High<br>Voltage                      | 4.5V                | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.8     | V     | Driven by External<br>Clock Generator  |       |

|                               |                                                  | 5.5V                | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.8     | V     | Driven by External<br>Clock Generator  |       |

| $V_{CL}$                      | Clock Input Low<br>Voltage                       | 4.5V                | V <sub>SS</sub> -0.3 | 0.2 V <sub>CC</sub>  | 1.7     | V     | Driven by External<br>Clock Generator  |       |

|                               |                                                  | 5.5V                | V <sub>SS</sub> -0.3 | 0.2 V <sub>CC</sub>  | 1.7     | V     | Driven by External<br>Clock Generator  |       |

| $V_{IH}$                      | Input High Voltage                               | 4.5V                | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.8     | V     |                                        |       |

|                               | -                                                | 5.5V                | $0.7\mathrm{V_{CC}}$ | V <sub>CC</sub> +0.3 | 2.8     | V     |                                        |       |

| $\overline{V_{IL}}$           | Input Low Voltage                                | 4.5V                | V <sub>SS</sub> -0.3 | 0.2 V <sub>CC</sub>  | 1.5     | V     |                                        |       |

|                               |                                                  | 5.5V                | V <sub>SS</sub> -0.3 | $0.2\mathrm{V_{CC}}$ | 1.5     | V     |                                        |       |

| V <sub>OH</sub>               | Output High Voltage                              | 4.5V                | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | $I_{OH} = -2.0 \text{ mA}$             | 5     |

|                               |                                                  | 5.5V                | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | $I_{OH} = -2.0 \text{ mA}$             | 5     |

|                               |                                                  | 4.5V                | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | Low Noise @ $I_{OH} = -0.5 \text{ mA}$ |       |

|                               | -                                                | 5.5V                | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | Low Noise @ $I_{OH} = -0.5 \text{ mA}$ |       |

| $V_{OL1}$                     | Output Low Voltage                               | 4.5V                |                      | 0.8                  | 0.1     | V     | I <sub>OL</sub> = +4.0 mA              | 5     |

|                               | -                                                | 5.5V                |                      | 0.4                  | 0.1     | V     | I <sub>OL</sub> = +4.0 mA              | 5     |

|                               | -                                                | 4.5V                |                      | 0.4                  | 0.1     | V     | Low Noise @ I <sub>OL</sub> = 1.0 mA   | -     |

|                               | -                                                | 5.5V                |                      | 0.4                  | 0.1     | V     | Low Noise @ I <sub>OL</sub> = 1.0 mA   |       |

| $\overline{V_{OL2}}$          | Output Low Voltage                               | 4.5V                |                      | 0.8                  | 8.0     | V     | I <sub>OL</sub> = +12 mA,              | 5     |

|                               | -                                                | 5.5V                |                      | 0.8                  | 0.8     | V     | I <sub>OL</sub> = +12 mA,              | 5     |

| $\overline{V_{OFFSET}}$       | Comparator Input                                 | 4.5V                |                      | 25.0                 | 10.0    | mV    |                                        |       |

|                               | Offset Voltage                                   | 5.5V                |                      | 25.0                 | 10.0    | mV    |                                        |       |

| $V_{LV}$                      | V <sub>CC</sub> Low Voltage<br>Auto Reset        |                     | 2.2                  | 3.0                  | 2.8     | V     | @ 6 MHz Max.<br>Int. CLK Freq.         |       |

| I <sub>IL</sub>               | Input Leakage                                    | 4.5V                | -1.0                 | 1.0                  |         | μΑ    | $V_{IN} = 0V, V_{CC}$                  |       |

|                               | (Input Bias Current of Comparator)               | 5.5V                | -1.0                 | 1.0                  |         | μΑ    | $V_{IN} = 0V, V_{CC}$                  |       |

| I <sub>OL</sub>               | Output Leakage                                   | 4.5V                | -1.0                 | 1.0                  |         | μΑ    | V <sub>IN</sub> = 0V, V <sub>CC</sub>  |       |

| -                             | -                                                | 5.5V                | -1.0                 | 1.0                  |         | μA    | $V_{IN} = 0V, V_{CC}$                  |       |

| $\overline{V_{ICR}}$          | Comparator Input<br>Common Mode<br>Voltage Range |                     | 0                    | V <sub>CC</sub> -1.0 |         | V     |                                        |       |

|                  |                                    |                     | T <sub>A</sub> = 0°C | to +70°C | Typical |       |                                                             |       |

|------------------|------------------------------------|---------------------|----------------------|----------|---------|-------|-------------------------------------------------------------|-------|

| Sym              | Parameter                          | V <sub>CC</sub> [4] | Min                  | Max      | @ 25°C  | Units | Conditions                                                  | Notes |

| I <sub>cc</sub>  | Supply Current                     | 4.5V                |                      | 11.0     | 6.8     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 5,7   |

|                  |                                    | 5.5V                |                      | 11.0     | 6.8     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 5,7   |

|                  |                                    | 4.5V                |                      | 15.0     | 8.2     | mA    | All Output and I/O Pins Floating @ 8 MHz                    | 5,7   |

|                  |                                    | 5.5V                |                      | 15.0     | 8.2     | mA    | All Output and I/O Pins Floating @ 8 MHz                    | 5,7   |

|                  |                                    | 4.5V                |                      | 20.0     | 12.0    | mA    | All Output and I/O Pins Floating @ 12 MHz                   | 5,7   |

|                  |                                    | 5.5V                |                      | 20.0     | 12.0    | mA    | All Output and I/O Pins Floating @ 12 MHz                   | 5,7   |

| I <sub>CC1</sub> | Standby Current                    | 4.5V                |                      | 4.0      | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 2 MHz                  | 5,7   |

|                  |                                    | 5.5V                |                      | 4.0      | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 2 MHz                  | 5,7   |

|                  |                                    | 4.5V                |                      | 5.0      | 3.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 8 MHz  | 5,7   |

|                  |                                    | 5.5V                |                      | 5.0      | 3.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 8 MHz  | 5,7   |

|                  |                                    | 4.5V                |                      | 7.0      | 4.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 12 MHz | 5,7   |

|                  |                                    | 5.5V                |                      | 7.0      | 4.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 12 MHz | 5,7   |

| I <sub>cc</sub>  | Supply Current<br>(Low Noise Mode) | 4.5V                |                      | 11.0     | 6.8     | mA    | All Output and I/O Pins Floating @ 1 MHz                    | 7     |

|                  |                                    | 5.5V                |                      | 11.0     | 6.8     | mA    | All Output and I/O Pins Floating @ 1 MHz                    | 7     |

|                  |                                    | 4.5V                |                      | 13.0     | 7.5     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 7     |

|                  |                                    | 5.5V                |                      | 13.0     | 7.5     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 7     |

|                  |                                    | 4.5V                |                      | 15.0     | 8.2     | mA    | All Output and I/O Pins Floating @ 4 MHz                    | 7     |

|                  |                                    | 5.5V                |                      | 15.0     | 8.2     | mA    | All Output and I/O Pins Floating @ 4 MHz                    | 7     |

# DC ELECTRICAL CHARACTERISTICS (Continued)

|                      |                  |                     | $T_A = 0^{\circ}$ | C to +70°C | Typical |       |                                 |       |

|----------------------|------------------|---------------------|-------------------|------------|---------|-------|---------------------------------|-------|

| Sym                  | Parameter        | V <sub>CC</sub> [4] | Min               | Max        | @ 25°C  | Units | Conditions                      | Notes |

| $\overline{I_{CC1}}$ | Standby Current  | 4.5V                |                   | 4.0        | 2.5     | mA    | HALT Mode V <sub>IN</sub> = 0V, | 7     |

|                      | (Low Noise Mode) |                     |                   |            |         |       | V <sub>CC</sub> @ 1 MHz         |       |

|                      |                  | 5.5V                |                   | 4.0        | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ ,       | 7     |

|                      |                  |                     |                   |            |         |       | V <sub>CC</sub> @ 1 MHz         |       |

|                      |                  | 4.5V                |                   | 4.5        | 2.8     | mA    | HALT Mode $V_{IN} = 0V$ ,       | 7     |

|                      |                  |                     |                   |            |         |       | V <sub>CC</sub> @ 2 MHz         |       |

|                      |                  | 5.5V                |                   | 4.5        | 2.8     | mA    | HALT Mode V <sub>IN</sub> = 0V, | 7     |

|                      |                  |                     |                   |            |         |       | V <sub>CC</sub> @ 2 MHz         |       |

|                      |                  | 4.5V                |                   | 5.0        | 3.0     | mA    | HALT Mode V <sub>IN</sub> = 0V, | 7     |

|                      |                  |                     |                   |            |         |       | V <sub>CC</sub> @ 4 MHz         |       |

|                      |                  | 5.5V                |                   | 5.0        | 3.0     | mA    | HALT Mode $V_{IN} = 0V$ ,       | 7     |

|                      |                  |                     |                   |            |         |       | V <sub>CC</sub> @ 4 MHz         |       |

| I <sub>CC2</sub>     | Standby Current  | 4.5V                |                   | 10.0       | 1.0     | μΑ    | STOP Mode $V_{IN} = 0V, V_{CC}$ | 7,8   |

|                      |                  |                     |                   |            |         |       | WDT is not Running              |       |

|                      |                  | 5.5V                |                   | 10.0       | 1.0     | μΑ    | STOP Mode $V_{IN} = 0V, V_{CC}$ | 7,8   |

|                      |                  |                     |                   |            |         |       | WDT is not Running              |       |

| I <sub>ALL</sub>     | Auto Latch Low   | 4.5V                |                   | 32.0       | 16      | μΑ    | $0V < V_{IN} < V_{CC}$          |       |

|                      | Current          | 5.5V                |                   | 32.0       | 16      | μΑ    | $0V < V_{IN} < V_{CC}$          |       |

| I <sub>ALH</sub>     | Auto Latch High  | 4.5V                |                   | -16.0      | -8.0    | μΑ    | $0V < V_{IN} < V_{CC}$          |       |

|                      | Current          | 5.5V                |                   | -16.0      | -8.0    | μΑ    | $0V < V_{IN} < V_{CC}$          |       |

#### Notes:

- 1. Port 2 and Port 0 only

- 2.  $V_{SS} = 0V = GND$

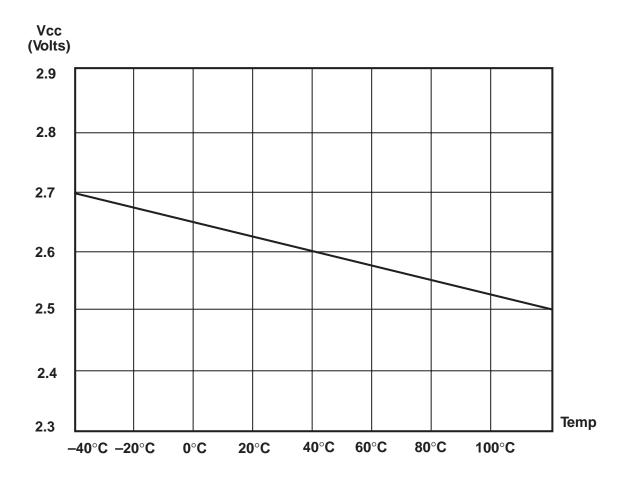

- 3. The device operates down to  $V_{LV}$  of the specified frequency for  $V_{LV}$ . The minimum operational  $V_{CC}$  is determined on the value of the voltage  $V_{LV}$  at the ambient temperature. The  $V_{LV}$  increases as the temperature decreases.

- 4.  $V_{CC}$  = 4.5 to 5.5V, typical values measured at  $V_{CC}$  = 5.0V. The  $V_{CC}$  voltage specification of 5.5 V guarantees 5.0 V  $\pm$  0.5V with typical values measured at  $V_{CC}$  = 5.0V.

- 5. Standard Mode (not Low EMI Mode)

- 6. Z86E08 only

- 7. All outputs unloaded and all inputs are at  $\rm V_{\rm CC}$  or  $\rm V_{\rm SS}$  level.

- 8. If analog comparator is selected, then the comparator inputs must be at  $V_{\text{CC}}$  level.

**Extended Temperature**

|                               |                                                  |                     |                             | 40°C to<br>95°C      | Typical |       |                                        |       |

|-------------------------------|--------------------------------------------------|---------------------|-----------------------------|----------------------|---------|-------|----------------------------------------|-------|

| Sym                           | Parameter                                        | V <sub>CC</sub> [4] | Min                         | Max                  | @ 25°C  | Units | Conditions                             | Notes |

| $\overline{V_{\text{INMAX}}}$ | Max Input Voltage                                | 4.5V                |                             | 12.0                 |         | V     | I <sub>IN</sub> < 250 μA               | 1     |

|                               |                                                  | 5.5V                |                             | 12.0                 |         | V     | I <sub>IN</sub> < 250 μA               | 1     |

| V <sub>CH</sub>               | Clock Input High<br>Voltage                      | 4.5V                | 0.8 V <sub>CC</sub>         | V <sub>CC</sub> +0.3 | 2.8     | V     | Driven by External<br>Clock Generator  |       |

|                               |                                                  | 5.5V                | 0.8 V <sub>CC</sub>         | V <sub>CC</sub> +0.3 | 2.8     | V     | Driven by External<br>Clock Generator  |       |

| V <sub>CL</sub>               | Clock Input Low<br>Voltage                       | 4.5V                | V <sub>SS</sub> -0.3        | 0.2 V <sub>CC</sub>  | 1.7     | V     | Driven by External<br>Clock Generator  |       |

|                               |                                                  | 5.5V                | V <sub>SS</sub> -0.3        | 0.2 V <sub>CC</sub>  | 1.7     | V     | Driven by External<br>Clock Generator  |       |

| V <sub>IH</sub>               | Input High Voltage                               | 4.5V                | $0.7\mathrm{V}_\mathrm{CC}$ | V <sub>CC</sub> +0.3 | 2.8     | V     |                                        |       |

|                               |                                                  | 5.5V                | 0.7 V <sub>CC</sub>         | V <sub>CC</sub> +0.3 | 2.8     | V     |                                        |       |

| V <sub>IL</sub>               | Input Low Voltage                                | 4.5V                | V <sub>SS</sub> -0.3        | 0.2 V <sub>CC</sub>  | 1.5     | V     |                                        |       |

|                               |                                                  | 5.5V                | V <sub>SS</sub> -0.3        | 0.2 V <sub>CC</sub>  | 1.5     | V     |                                        |       |

| V <sub>OH</sub>               | Output High Voltage                              | 4.5V                | V <sub>CC</sub> -0.4        |                      | 4.8     | V     | $I_{OH} = -2.0 \text{ mA}$             | 5     |

|                               |                                                  | 5.5V                | V <sub>CC</sub> -0.4        |                      | 4.8     | V     | $I_{OH} = -2.0 \text{ mA}$             | 5     |

|                               |                                                  | 4.5V                | V <sub>CC</sub> -0.4        |                      |         | V     | Low Noise @ $I_{OH} = -0.5 \text{ mA}$ |       |

|                               |                                                  | 5.5V                | V <sub>CC</sub> -0.4        |                      |         | V     | Low Noise @ $I_{OH} = -0.5 \text{ mA}$ |       |

| $\overline{V_{OL1}}$          | Output Low Voltage                               | 4.5V                |                             | 0.4                  | 0.1     | V     | $I_{OL} = +4.0 \text{ mA}$             | 5     |

|                               |                                                  | 5.5V                |                             | 0.4                  | 0.1     | V     | $I_{OL} = +4.0 \text{ mA}$             | 5     |

|                               |                                                  | 4.5V                |                             | 0.4                  | 0.1     | V     | Low Noise @ I <sub>OL</sub> = 1.0 mA   |       |

|                               |                                                  | 5.5V                |                             | 0.4                  | 0.1     | V     | Low Noise @ I <sub>OL</sub> = 1.0 mA   |       |

| $\overline{V_{OL2}}$          | Output Low Voltage                               | 4.5V                |                             | 1.0                  | 0.3     | V     | I <sub>OL</sub> = +12 mA,              | 5     |

|                               |                                                  | 5.5V                |                             | 1.0                  | 0.3     | V     | I <sub>OL</sub> = +12 mA,              | 5     |

| $\overline{V_{OFFSET}}$       | Comparator Input                                 | 4.5V                |                             | 25.0                 | 10.0    | mV    |                                        |       |

|                               | Offset Voltage                                   | 5.5V                |                             | 25.0                 | 10.0    | mV    |                                        |       |

| $V_{LV}$                      | V <sub>CC</sub> Low Voltage<br>Auto Reset        |                     | 1.8                         | 3.8                  | 2.8     | V     | @ 6 MHz Max. Int.<br>CLK Freq.         | 3     |

| I <sub>IL</sub>               | Input Leakage                                    | 4.5V                |                             | -1.0                 | 1.0     | μΑ    | $V_{IN} = 0V, V_{CC}$                  |       |

|                               | (Input Bias Current of Comparator)               | 5.5V                |                             | -1.0                 | 1.0     | μΑ    | $V_{IN} = 0V, V_{CC}$                  |       |

| $I_{OL}$                      | Output Leakage                                   | 4.5V                |                             | -1.0                 | 1.0     | μΑ    | $V_{IN} = 0V, V_{CC}$                  |       |

|                               |                                                  | 5.5V                |                             | -1.0                 | 1.0     | μΑ    | $V_{IN} = 0V, V_{CC}$                  |       |

| V <sub>ICR</sub>              | Comparator Input<br>Common Mode<br>Voltage Range |                     | 0                           | V <sub>CC</sub> –1.5 |         | V     |                                        |       |

# DC ELECTRICAL CHARACTERISTICS (Continued)

|                  |                                    |                     | T <sub>A</sub> = -4<br>+10 |      | Typical |       |                                                             |       |

|------------------|------------------------------------|---------------------|----------------------------|------|---------|-------|-------------------------------------------------------------|-------|

| Sym              | Parameter                          | V <sub>CC</sub> [4] | Min                        | Max  | @ 25°C  | Units | Conditions                                                  | Notes |

| I <sub>CC</sub>  | Supply Current                     | 4.5V                |                            | 11.0 | 6.8     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 5,7   |

|                  |                                    | 5.5V                |                            | 11.0 | 6.8     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 5,7   |

|                  |                                    | 4.5V                |                            | 15.0 | 8.2     | mA    | All Output and I/O Pins Floating @ 8 MHz                    | 5,7   |

|                  |                                    | 5.5V                |                            | 15.0 | 8.2     | mA    | All Output and I/O Pins Floating @ 8 MHz                    | 5,7   |

|                  |                                    | 4.5V                |                            | 20.0 | 12.0    | mA    | All Output and I/O Pins Floating @ 12 MHz                   | 5,7   |

|                  |                                    | 5.5V                |                            | 20.0 | 12.0    | mA    | All Output and I/O Pins Floating @ 12 MHz                   | 5,7   |

| I <sub>CC1</sub> | Standby Current                    | 4.5V                |                            | 5.0  | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 2 MHz                  | 5,7   |

|                  |                                    | 5.5V                |                            | 5.0  | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 2 MHz                  | 5,7   |

|                  |                                    | 4.5V                |                            | 5.0  | 3.0     | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 8 MHz                  | 5,7   |

|                  |                                    | 5.5V                |                            | 5.0  | 3.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 8 MHz  | 5,7   |

|                  |                                    | 4.5V                |                            | 7.0  | 4.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 12 MHz | 5,7   |

|                  |                                    | 5.5V                |                            | 7.0  | 4.0     | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 12 MHz                 | 5,7   |

| I <sub>CC</sub>  | Supply Current<br>(Low Noise Mode) | 4.5V                |                            | 11.0 | 6.8     | mA    | All Output and I/O Pins Floating @ 1 MHz                    | 7     |

|                  |                                    | 5.5V                |                            | 11.0 | 6.8     | mA    | All Output and I/O Pins Floating @ 1 MHz                    | 7     |

|                  |                                    | 4.5V                |                            | 13.0 | 7.5     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 7     |

|                  |                                    | 5.5V                |                            | 13.0 | 7.5     | mA    | All Output and I/O Pins Floating @ 2 MHz                    | 7     |

|                  |                                    | 4.5V                |                            | 15.0 | 8.2     | mA    | All Output and I/O Pins Floating @ 4 MHz                    | 7     |

|                  |                                    | 5.5V                |                            | 15.0 | 8.2     | mA    | All Output and I/O Pins Floating @ 4 MHz                    | 7     |

| Sym              | Parameter                        | V <sub>CC</sub> [4] | $T_A = -40^{\circ}C$ to $+105^{\circ}C$<br>Min Max | Typical<br>@ 25°C | Units | Conditions                                                 | Notes |

|------------------|----------------------------------|---------------------|----------------------------------------------------|-------------------|-------|------------------------------------------------------------|-------|

| I <sub>CC1</sub> | Standby Current (Low Noise Mode) | 4.5V                | 4.0                                                | 2.5               | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 1 MHz | 7     |

|                  |                                  | 5.5V                | 4.0                                                | 2.5               | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 1 MHz                 | 7     |

|                  |                                  | 4.5V                | 4.5                                                | 2.8               | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 2 MHz                 | 7     |

|                  |                                  | 5.5V                | 4.5                                                | 2.8               | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 2 MHz                 | 7     |

|                  |                                  | 4.5V                | 5.0                                                | 3.0               | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 4 MHz                 | 7     |

|                  |                                  | 5.5V                | 5.0                                                | 3.0               | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC}$ @ 4 MHz                 | 7     |

| I <sub>CC2</sub> | Standby Current                  | 4.5V                | 20                                                 | 1.0               | μΑ    | STOP Mode $V_{IN} = 0V, V_{CC}$<br>WDT is not Running      | 7,8   |

|                  |                                  | 5.5V                | 20                                                 | 1.0               | μΑ    | STOP Mode $V_{IN} = 0V, V_{CC}$<br>WDT is not Running      | 7,8   |

| I <sub>ALL</sub> | Auto Latch Low                   | 4.5V                | 40                                                 | 16                | μΑ    | $0V < V_{IN} < V_{CC}$                                     |       |

|                  | Current                          | 5.5V                | 40                                                 | 16                | μΑ    | $0V < V_{IN} < V_{CC}$                                     |       |

| I <sub>ALH</sub> | Auto Latch High                  | 4.5V                | -20.0                                              | -8.0              | μΑ    | $0V < V_{IN} < V_{CC}$                                     |       |

|                  | Current                          | 5.5V                | -20.0                                              | -8.0              | μΑ    | $0V < V_{IN} < V_{CC}$                                     |       |

#### Notes:

- 1. Port 2 and Port 0 only

- 2.  $V_{SS} = 0V = GND$

- 3. The device operates down to  $V_{LV}$  of the specified frequency for  $V_{LV}$ . The minimum operational  $V_{CC}$  is determined on the value of the voltage  $V_{LV}$  at the ambient temperature. The  $V_{LV}$  increases as the temperature decreases.

- 4.  $V_{CC}$  = 4.5V to 5.5V, typical values measured at  $V_{CC}$  = 5.0V

- 5. Standard Mode (not Low EMI Mode)

- 6. Z86E08 only

- 7. All outputs unloaded and all inputs are at  $\rm V_{CC}$  or  $\rm V_{SS}$  level.

- 8. If analog comparator is selected, then the comparator inputs must be at  $V_{\text{CC}}$  level.

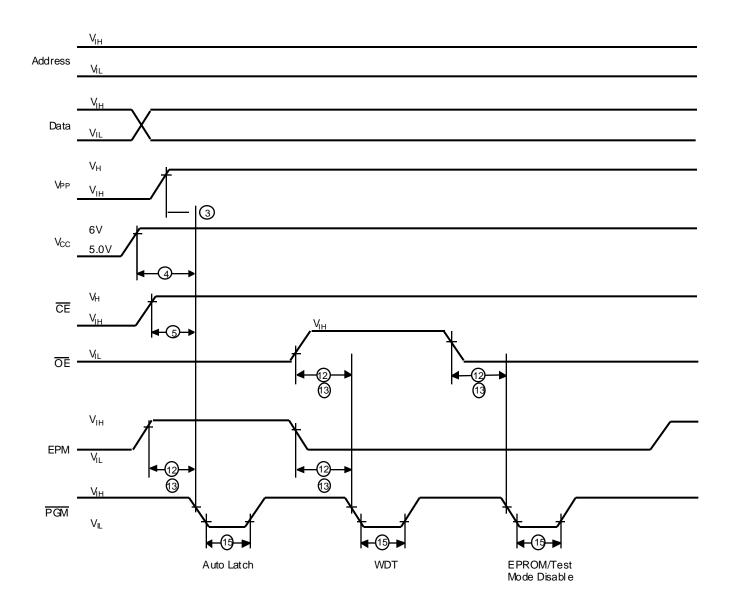

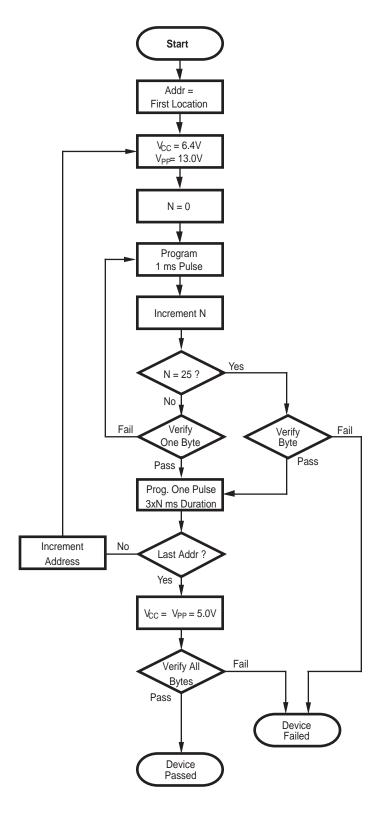

Figure 6. AC Electrical Timing Diagram

Timing Table (Standard Mode for SCLK/TCLK = XTAL/2) Standard Temperature

| 15 |         |                        |          | Т    | <sub>A</sub> = 0 °C 1 | to +70 °C | ;   |       |       |

|----|---------|------------------------|----------|------|-----------------------|-----------|-----|-------|-------|

|    |         |                        |          | 8 M  | Hz                    | 12 I      | ИНz |       |       |

| No | Symbol  | Parameter              | $V_{CC}$ | Min  | Max                   | Min       | Max | Units | Notes |

| 1  | ТрС     | Input Clock Period     | 4.5V     | 125  | DC                    | 83        | DC  | ns    | 1     |

|    |         |                        | 5.5V     | 125  | DC                    | 83        | DC  | ns    | 1     |

| 2  | TrC,TfC | Clock Input Rise       | 4.5V     |      | 25                    |           | 15  | ns    | 1     |

|    |         | and Fall Times         | 5.5V     |      | 25                    |           | 15  | ns    | 1     |

| 3  | TwC     | Input Clock Width      | 4.5V     | 62   |                       | 41        |     | ns    | 1     |

|    |         |                        | 5.5V     | 62   |                       | 41        |     | ns    | 1     |

| 4  | TwTinL  | Timer Input Low Width  | 4.5V     | 100  |                       | 100       |     | ns    | 1     |

|    |         |                        | 5.5V     | 70   |                       | 70        |     | ns    | 1     |

| 5  | TwTinH  | Timer Input High Width | 4.5V     | 5TpC |                       | 5TpC      |     |       | 1     |

|    |         |                        | 5.5V     | 5TpC |                       | 5TpC      |     |       | 1     |

| 6  | TpTin   | Timer Input Period     | 4.5V     |      | 8TpC                  | 8TpC      |     |       | 1     |

|    |         |                        | 5.5V     |      | 8TpC                  | 8TpC      |     |       | 1     |

| 7  | TrTin,  | Timer Input Rise       | 4.5V     |      | 100                   |           | 100 | ns    | 1     |

|    | TtTin   | and Fall Time          | 5.5V     |      | 100                   |           | 100 | ns    | 1     |

| 8  | TwIL    | Int. Request Input     | 4.5V     | 70   |                       | 70        |     | ns    | 1,2   |

|    |         | Low Time               | 5.5V     | 70   |                       | 70        |     | ns    | 1,2   |

| 9  | TwIH    | Int. Request Input     | 4.5V     |      | 5TpC                  | 5TpC      |     |       | 1,2   |

|    |         | High Time              | 5.5V     |      | 5TpC                  | 5TpC      |     |       | 1,2   |

| 10 | Twdt    | Watch-Dog Timer        | 4.5V     | 12   |                       | 12        |     | ms    | 1     |

|    |         | Delay Time for Timeout | 5.5V     | 12   |                       | 12        |     | ms    | 1     |

| 11 | Tpor    | Power-On Reset Time    | 4.5V     | 20   | 80                    | 20        | 80  | ms    | 1     |

|    |         |                        | 5.5V     | 20   | 80                    | 20        | 80  | ms    | 1     |

#### Notes:

<sup>1.</sup> Timing Reference uses 0.7  $\rm V_{CC}$  for a logic 1 and 0.2  $\rm V_{CC}$  for a logic 0.

<sup>2.</sup> Interrupt request through Port 3 (P33-P31).

Timing Table (Standard Mode for SCLK/TCLK = XTAL/2) **Extended Temperature**

|    |         |                        |          | T<br>8 M |     | to +105 °C<br>12 N |     |       |       |

|----|---------|------------------------|----------|----------|-----|--------------------|-----|-------|-------|

| No | Symbol  | Parameter              | $v_{cc}$ | Min      | Max | Min                | Max | Units | Notes |

| 1  | ТрС     | Input Clock Period     | 4.5V     | 125      | DC  | 83                 | DC  | ns    | 1     |

|    |         | •                      | 5.5V     | 125      | DC  | 83                 | DC  | ns    | 1     |

| 2  | TrC,TfC | Clock Input Rise       | 4.5V     |          | 25  |                    | 15  | ns    | 1     |

|    |         | and Fall Times         | 5.5V     |          | 25  |                    | 15  | ns    | 1     |

| 3  | TwC     | Input Clock Width      | 4.5V     |          | 62  |                    | 41  | ns    | 1     |

|    |         | •                      | 5.5V     |          | 62  |                    | 41  | ns    | 1     |

| 4  | TwTinL  | Timer Input Low Width  | 4.5V     | 70       |     | 70                 |     | ns    | 1     |

|    |         |                        | 5.5V     | 70       |     | 70                 |     | ns    | 1     |

| 5  | TwTinH  | Timer Input High Width | 4.5V     | 5TpC     |     | 5TpC               |     |       | 1     |

|    |         | •                      | 5.5V     | 5TpC     |     | 5TpC               |     |       | 1     |

| 6  | TpTin   | Timer Input Period     | 4.5V     | 8TpC     |     | 8TpC               |     |       | 1     |

|    |         |                        | 5.5V     | 8TpC     |     | 8TpC               |     |       | 1     |

| 7  | TrTin,  | Timer Input Rise       | 4.5V     |          | 100 |                    | 100 | ns    | 1     |

|    | TtTin   | and Fall Time          | 5.5V     |          | 100 |                    | 100 | ns    | 1     |

| 8  | TwIL    | Int. Request Input     | 4.5V     | 70       |     | 70                 |     | ns    | 1,2   |

|    |         | Low Time               | 5.5V     | 70       |     | 70                 |     | ns    | 1,2   |

| 9  | TwIH    | Int. Request Input     | 4.5V     | 5TpC     |     | 5TpC               |     |       | 1,2   |

|    |         | High Time              | 5.5V     | 5TpC     |     | 5TpC               |     |       | 1,2   |

| 10 | Twdt    | Watch-Dog Timer        | 4.5V     | 10       |     | 10                 |     | ms    | 1     |

|    |         | Delay Time for Timeout | 5.5V     | 10       |     | 10                 |     | ms    | 1     |

| 11 | Tpor    | Power-On Reset Time    | 4.5V     | 12       | 100 | 12                 | 100 | ms    | 1     |

|    |         | ·                      | 5.5V     | 12       | 100 | 12                 | 100 | ms    | 1     |

Timing Reference uses 0.7 V<sub>CC</sub> for a logic 1 and 0.2 V<sub>CC</sub> for a logic 0.

Interrupt request made through Port 3 (P33–P31).

Low Noise Mode, Standard Temperature

|    |           |                        |          | Т      | _<br>A= 0 °C t | o +70 °C |     |       |       |

|----|-----------|------------------------|----------|--------|----------------|----------|-----|-------|-------|

|    |           |                        |          | 1 M    | Hz             | 4 M      | Hz  |       |       |

| No | Symbol    | Parameter              | $v_{cc}$ | Min    | Max            | Min      | Max | Units | Notes |

| 1  | TPC       | Input Clock Period     | 4.5V     | 1000   | DC             | 250      | DC  | ns    | 1     |

|    |           | <del>-</del>           | 5.5V     | 1000   | DC             | 250      | DC  | ns    | 1     |

| 2  | TrC       | Clock Input Rise       | 4.5V     |        | 25             |          | 25  | ns    | 1     |

|    | TfC       | and Fall Times         | 5.5V     |        | 25             |          | 25  | ns    | 1     |

| 3  | TwC       | Input Clock Width      | 4.5V     | 500    |                | 125      |     | ns    | 1     |

|    |           | -                      | 5.5V     | 500    |                | 125      |     | ns    | 1     |

| 4. | TwTinL    | Timer Input Low Width  | 4.5V     | 70     |                | 70       |     | ns    | 1     |

|    |           | <del>-</del>           | 5.5V     | 70     |                | 70       |     | ns    | 1     |

| 5  | TwTinH    | Timer Input High Width | 4.5V     | 2.5TpC |                | 2.5TpC   |     |       | 1     |

|    |           | <del>-</del>           | 5.5V     | 2.5TpC |                | 2.5TpC   |     |       | 1     |

| 6  | TpTin     | Timer Input Period     | 4.5V     | 4TpC   |                | 4TpC     |     |       | 1     |

|    |           | -                      | 5.5V     | 4TpC   |                | 4TpC     |     |       | 1     |

| 7  | TrTin,    | Timer Input Rise       | 4.5V     |        | 100            |          | 100 | ns    | 1     |

|    | TtTin     | and Fall Time          | 5.5V     |        | 100            |          | 100 | ns    | 1     |

| 8  | TwIL      | Int. Request Input     | 4.5V     | 70     |                | 70       |     | ns    | 1,2   |

|    | Low Time  | -                      | 5.5V     | 70     |                | 70       |     | ns    | 1,2   |

| 9  | TwIH      | Int. Request Input     | 4.5V     | 2.5TpC |                | 2.5TpC   |     |       | 1,2   |

|    | High Time | -                      | 5.5V     | 2.5TpC |                | 2.5TpC   |     |       | 1,2   |

| 10 | Twdt      | Watch-Dog Timer        | 4.5V     | 12     |                | 12       |     | ms    | 1     |

|    |           | Delay Time for Timeout | 5.5V     | 12     |                | 12       |     | ms    | 1     |

#### Notes:

<sup>1.</sup> Timing Reference uses 0.7  $\rm V_{\rm CC}$  for a logic 1 and 0.2  $\rm V_{\rm CC}$  for a logic 0.

<sup>2.</sup> Interrupt request through Port 3 (P33-P31).

# AC ELECTRICAL CHARACTERISTICS (Continued)

Low Noise Mode, Extended Temperature

|    |        |                        |          | T <sub>A</sub> | = −40 °C | to +105 ° | С   |       |       |

|----|--------|------------------------|----------|----------------|----------|-----------|-----|-------|-------|

|    |        |                        |          | 1 M            |          | 4 M       |     |       |       |

| No | Symbol | Parameter              | $V_{CC}$ | Min            | Max      | Min       | Max | Units | Notes |

| 1  | TPC    | Input Clock Period     | 4.5V     | 1000           | DC       | 250       | DC  | ns    | 1     |

|    |        |                        | 5.5V     | 1000           | DC       | 250       | DC  | ns    | 1     |

| 2  | TrC    | Clock Input Rise       | 4.5V     |                | 25       |           | 25  | ns    | 1     |

|    | TfC    | and Fall Times         | 5.5V     |                | 25       |           | 25  | ns    | 1     |

| 3  | TwC    | Input Clock Width      | 4.5V     | 500            |          | 125       |     | ns    | 1     |

|    |        |                        | 5.5V     | 500            |          | 125       |     | ns    | 1     |

| 4. | TwTinL | Timer Input Low Width  | 4.5V     | 70             |          | 70        |     | ns    | 1     |

|    |        |                        | 5.5V     | 70             |          | 70        |     | ns    | 1     |

| 5  | TwTinH | Timer Input High Width | 4.5V     | 2.5TpC         |          | 2.5TpC    |     |       | 1     |

|    |        |                        | 5.5V     | 2.5TpC         |          | 2.5TpC    |     |       | 1     |

| 6  | TpTin  | Timer Input Period     | 4.5V     |                | 4TpC     | 4TpC      |     |       | 1     |

|    |        |                        | 5.5V     |                | 4TpC     | 4TpC      |     |       | 1     |

| 7  | TrTin, | Timer Input Rise       | 4.5V     |                | 100      |           | 100 | ns    | 1     |

|    | TtTin  | and Fall Time          | 5.5V     |                | 100      |           | 100 | ns    | 1     |

| 8  | TwIL   | Int. Request Input     | 4.5V     | 70             |          | 70        |     | ns    | 1,2   |

|    |        | Low Time               | 5.5V     | 70             |          | 70        |     | ns    | 1,2   |

| 9  | TwIH   | Int. Request Input     | 4.5V     | 2.5TpC         |          | 2.5TpC    |     |       | 1,2   |

|    |        | High Time              | 5.5V     | 2.5TpC         |          | 2.5TpC    |     |       | 1,2   |

| 10 | Twdt   | Watch-Dog Timer        | 4.5V     | 10             |          | 10        |     | ms    | 1     |

|    |        | Delay Time for Timeout | 5.5V     | 10             |          | 10        |     | ms    | 1     |

#### Notes:

<sup>1.</sup> Timing Reference uses 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC}$  for a logic 0. 2. Interrupt request through Port 3 (P33–P31).

#### **LOW NOISE VERSION**

#### **Low EMI Emission**

The Z86E04/E08 can be programmed to operate in a Low EMI Emission Mode by means of a mask ROM bit option. Use of this feature results in:

- All pre-driver slew rates reduced to 10 ns typical.

- Internal SCLK/TCLK operation limited to a maximum of 4 MHz–250 ns cycle time.

- Output drivers have resistances of 500 Ohms (typical).

- Oscillator divide-by-two circuitry eliminated.

The Low EMI Mode is mask-programmable to be selected by the customer at the time the ROM code is submitted.

#### **PIN FUNCTIONS**

# **OTP Programming Mode**

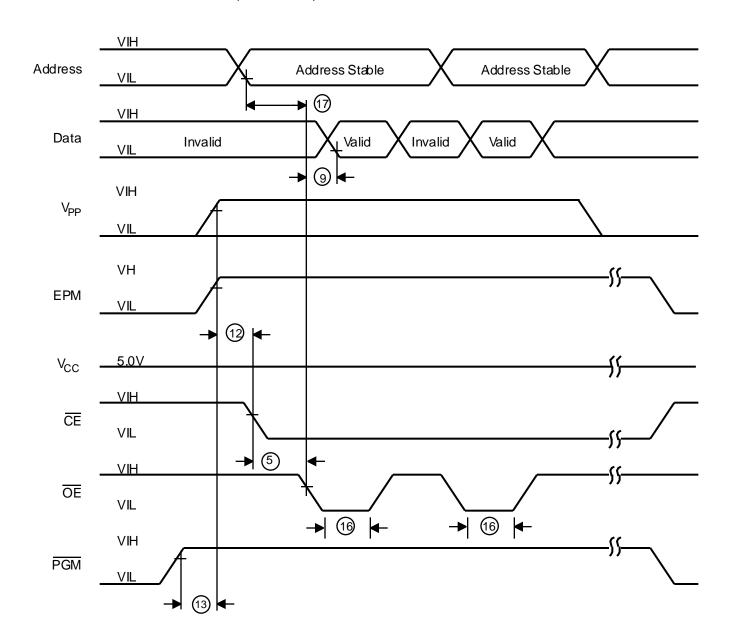

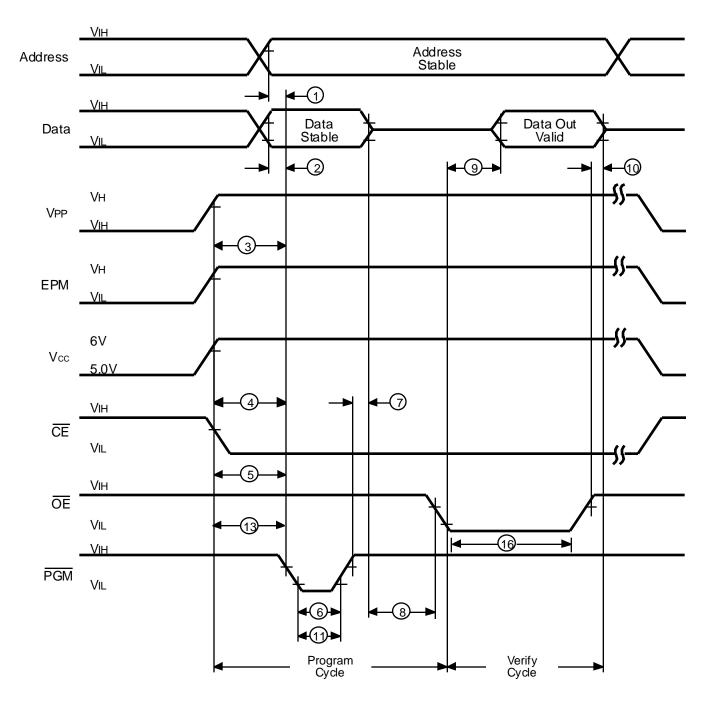

**D7–D0** Data Bus. Data can be read from, or written to, the EPROM through this data bus.

**V**<sub>CC</sub> *Power Supply.* It is typically 5V during EPROM Read Mode and 6.4V during the other modes (Program, Program Verify, and so on).

**CE** Chip Enable (active Low). This pin is active during EPROM Read Mode, Program Mode, and Program Verify Mode.

**OE** Output Enable (active Low). This pin drives the Data Bus direction. When this pin is Low, the Data Bus is output. When High, the Data Bus is input.

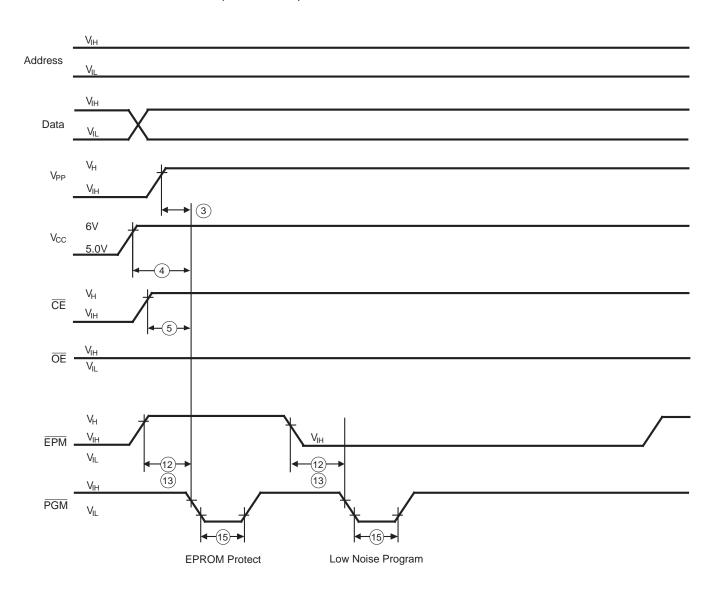

**EPM** *EPROM Program Mode.* This pin controls the different EPROM Program Modes by applying different voltages.

$\mathbf{V}_{\text{PP}}$  *Program Voltage.* This pin supplies the program voltage.

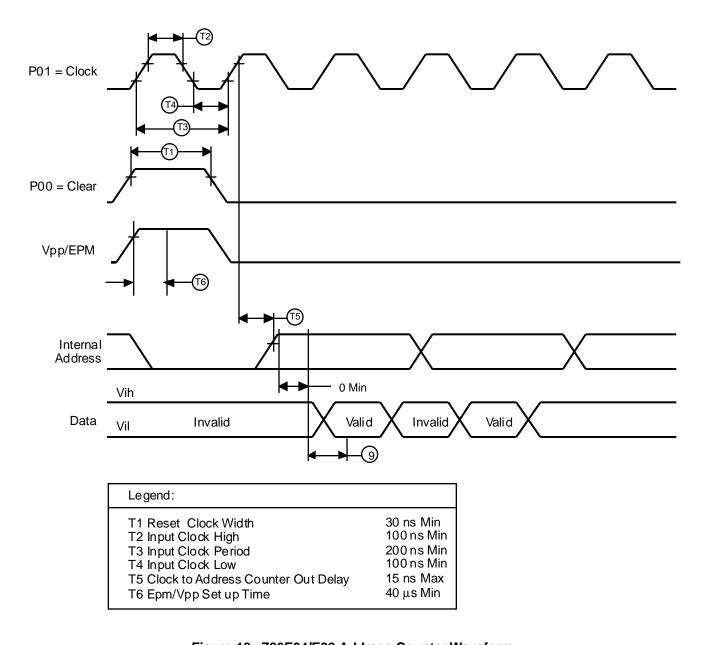

**Clear** Clear (active High). This pin resets the internal address counter at the High Level.

**Clock** *Address Clock*. This pin is a clock input. The internal address counter increases by one with one clock cycle.

**PGM** *Program Mode* (active Low). A Low level at this pin programs the data to the EPROM through the Data Bus.

# **Application Precaution**

The production test-mode environment may be enabled accidentally during normal operation if *excessive noise* surges above V<sub>CC</sub> occur on the XTAL1 pin.

In addition, processor operation of Z8 OTP devices may be affected by *excessive noise* surges on the V<sub>PP</sub>,  $\overline{\text{CE}}$ , EPM,  $\overline{\text{OE}}$  pins while the microcontroller is in Standard Mode.

Recommendations for dampening voltage surges in both test and OTP Mode include the following:

- Using a clamping diode to V<sub>CC</sub>.

- Adding a capacitor to the affected pin.

**Note:** Programming the EPROM/Test Mode Disable option will prevent accidental entry into EPROM Mode or Test Mode.

# **PIN FUNCTIONS** (Continued)

**XTAL1, XTAL2** *Crystal In, Crystal Out* (time-based input and output, respectively). These pins connect a parallel-resonant crystal, LC, or an external single-phase clock (8 MHz or 12 MHz max) to the on-chip clock oscillator and buffer.

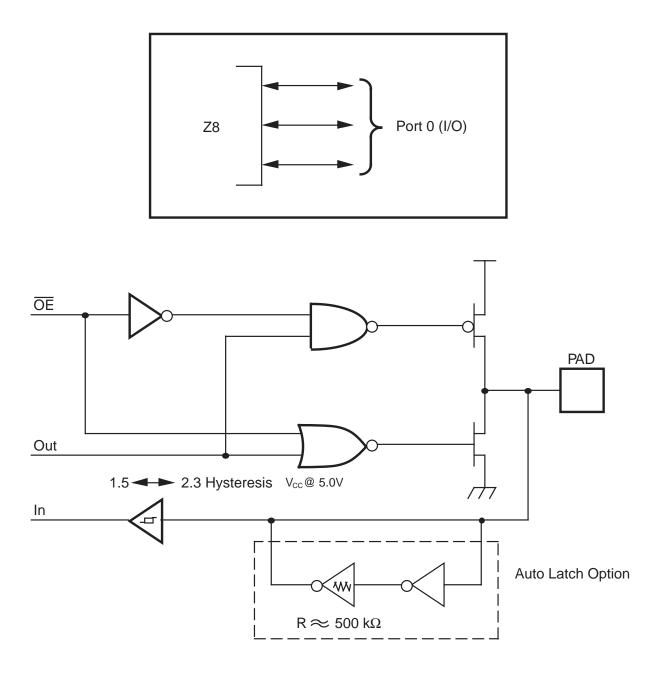

**Port 0, P02–P00.** Port 0 is a 3-bit bidirectional, Schmitt-triggered CMOS-compatible I/O port. These three I/O lines can be globally configured under software control to be inputs or outputs (Figure 7).

Auto Latch. The Auto Latch puts valid CMOS levels on all CMOS inputs (except P33, P32, P31) that are not externally driven. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer. On Power-up and Reset, the Auto Latch will set the ports to an undetermined state of 0 or 1. Default condition is Auto Latches enabled.

Figure 7. Port 0 Configuration

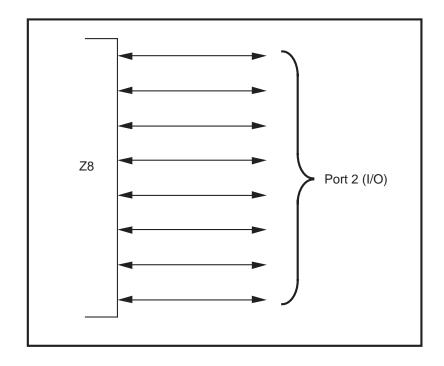

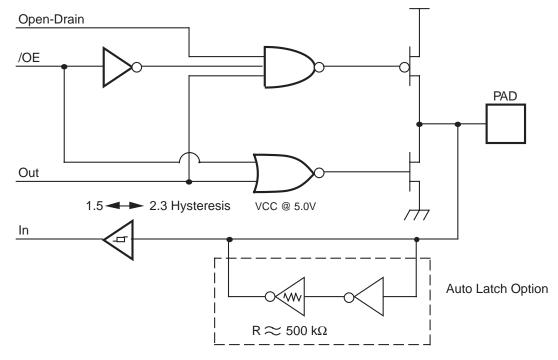

**Port 2, P27–P20.** Port 2 is an 8-bit, bit programmable, bidirectional, Schmitt-triggered CMOS-compatible I/O port. These eight I/O lines can be configured under software

control to be inputs or outputs, independently. Bits programmed as outputs can be globally programmed as either push-pull or open-drain (Figure 8).

Figure 8. Port 2 Configuration

# **PIN FUNCTIONS** (Continued)

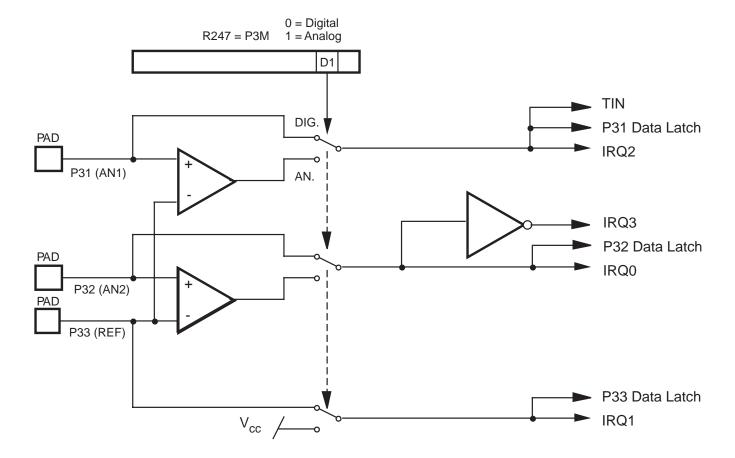

**Port 3, P33–P31**. Port 3 is a 3-bit, CMOS-compatible port with three fixed input (P33–P31) lines. These three input lines can be configured under software control as digital Schmitt-trigger inputs or analog inputs.

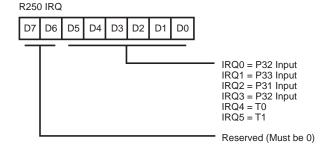

These three input lines are also used as the interrupt sources IRQ0–IRQ3, and as the timer input signal  $T_{\rm IN}$  (Figure 9).

Figure 9. Port 3 Configuration

IRQ3

IRQ 0,1,2 = Falling Edge Detection

= Rising Edge Detection

**Comparator Inputs.** Two analog comparators are added to input of Port 3, P31, and P32, for interface flexibility. The comparators reference voltage P33 (REF) is common to both comparators.

Typical applications for the on-board comparators; Zero crossing detection, A/D conversion, voltage scaling, and threshold detection. In Analog Mode, P33 input functions serve as a reference voltage to the comparators.

The dual comparator (common inverting terminal) features a single power supply which discontinues power in STOP

Mode. The common voltage range is 0–4 V when the  $V_{\rm CC}$  is 5.0V; the power supply and common mode rejection ratios are 90 dB and 60 dB, respectively.

Interrupts are generated on either edge of Comparator 2's output, or on the falling edge of Comparator 1's output. The comparator output is used for interrupt generation, Port 3 data inputs, or  $T_{\rm IN}$  through P31. Alternatively, the comparators can be disabled, freeing the reference input (P33) for use as IRQ1 and/or P33 input.

#### **FUNCTIONAL DESCRIPTION**

The following special functions have been incorporated into the Z8 devices to enhance the standard Z8 core architecture to provide the user with increased design flexibility.

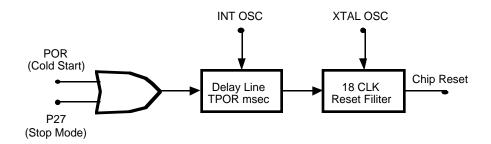

**RESET.** This function is accomplished by means of a Power-On Reset or a Watch-Dog Timer Reset. Upon power-up, the Power-On Reset circuit waits for  $T_{POR}$  ms, plus 18 clock cycles, then starts program execution at address 000C (Hex) (Figure 10). The Z8 control registers' reset value is shown in Table 3.

Figure 10. Internal Reset Configuration

**Power-On Reset (POR).** A timer circuit clocked by a dedicated on-board RC oscillator is used for a POR timer function. The POR time allows  $V_{CC}$  and the oscillator circuit to stabilize before instruction execution begins. The POR timer circuit is a one-shot timer triggered by one of the four following conditions:

- Power-bad to power-good status

- Stop-Mode Recovery

- WDT time-out

- WDH time-out

**Watch-Dog Timer Reset.** The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT is initially enabled by executing the WDT instruction and is retriggered on subsequent execution of the WDT instruction. The timer circuit is driven by an on-board RC oscillator.

**Table 3. Control Registers**

|       |       |    |    | R  | eset C | onditio | n  |    |    |                                          |

|-------|-------|----|----|----|--------|---------|----|----|----|------------------------------------------|

| Addr. | Reg.  | D7 | D6 | D5 | D4     | D3      | D2 | D1 | D0 | Comments                                 |

| FF    | SPL   | 0  | 0  | 0  | 0      | 0       | 0  | 0  | 0  |                                          |

| FD    | RP    | 0  | 0  | 0  | 0      | 0       | 0  | 0  | 0  |                                          |

| FC    | FLAGS | U  | U  | U  | U      | U       | U  | U  | U  |                                          |

| FB    | IMR   | 0  | U  | U  | U      | U       | U  | U  | U  |                                          |

| FA    | IRQ   | U  | U  | 0  | 0      | 0       | 0  | 0  | 0  | IRQ3 is used for positive edge detection |

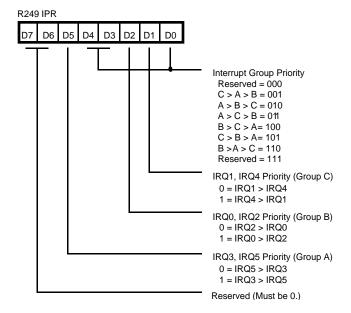

| F9    | IPR   | U  | U  | U  | U      | U       | U  | U  | U  |                                          |

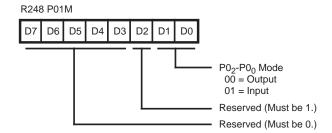

| F8*   | P01M  | U  | U  | U  | 0      | U       | U  | 0  | 1  |                                          |

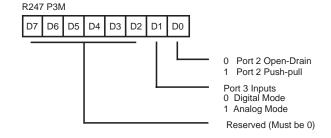

| F7*   | P3M   | U  | U  | U  | U      | U       | U  | 0  | 0  |                                          |

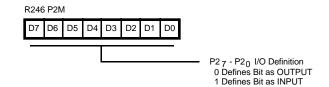

| F6*   | P2M   | 1  | 1  | 1  | 1      | 1       | 1  | 1  | 1  | Inputs after reset                       |

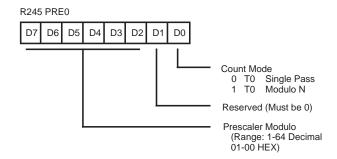

| F5    | PRE0  | U  | U  | U  | U      | U       | U  | U  | 0  |                                          |

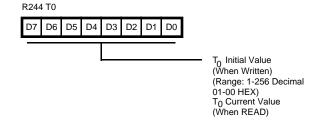

| F4    | T0    | U  | U  | U  | U      | U       | U  | U  | U  |                                          |

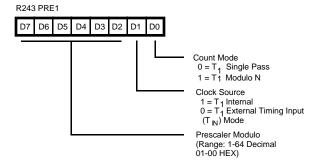

| F3    | PRE1  | U  | U  | U  | U      | U       | U  | 0  | 0  |                                          |

| F2    | T1    | U  | U  | U  | U      | U       | U  | U  | U  |                                          |

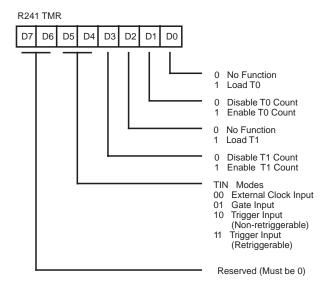

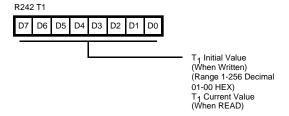

| F1    | TMR   | 0  | 0  | 0  | 0      | 0       | 0  | 0  | 0  |                                          |

**Note:** \*Registers are not reset after a STOP-Mode Recovery using P27 pin. A subsequent reset will cause these control registers to be reconfigured as shown in Table 4 and the user must avoid bus contention on the port pins or it may affect device reliability.

**Program Memory.** The Z86E04/E08 addresses up to 1K/2KB of Internal Program Memory (Figure 11). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. Bytes 0–1024/2048 are on-chip one-time programmable ROM.

Identifiers 1023/2047 3FFH/7FFH Location of On-Chip First Byte of ROM Instruction Executed After RESET 0CH 12 0BH 11 IRQ5 IRQ5 10 0AH IRQ4 09H 9 IRQ4 08H 8 7 07H IRQ3 Interrupt Vector 6 06H IRQ3 (Lower Byte) 5 IRQ2 05H 4 IRQ2 04H Interrupt Vector 3 IRQ1 03H (Upper Byte) 2 IRQ1 02H 1 IRQ0 01H 0 IRQ0 00H

Figure 11. Program Memory Map

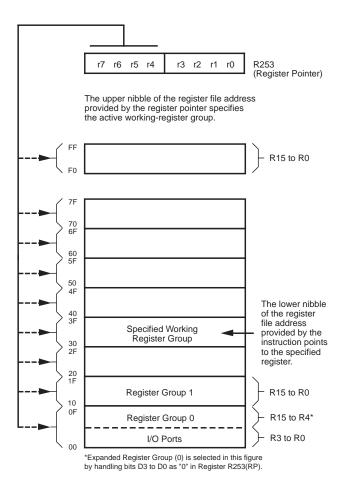

**Register File**. The Register File consists of three I/O port registers, 124 general-purpose registers, and 14 control and status registers R0–R3, R4–R127 and R241–R255, respectively (Figure 12). General-purpose registers occupy the 04H to 7FH address space. I/O ports are mapped as per the existing CMOS Z8.

| 255 (FFH)         Stack Pointer (Bits 7-0)         SPL           254 (FE)         General-Purpose Register         GPR           253 (FD)         Register Pointer         RP           252 (FC)         Program Control Flags         FLAGS           251 (FB)         Interrupt Mask Register         IMR           250 (FA)         Interrupt Request Register         IRQ           249 (F9)         Interrupt Priority Register         IPR           248 (F8)         Ports 0-1 Mode         P01M           247 (F7)         Port 3 Mode         P3M           246 (F6)         Port 2 Mode         P2M           245 (F5)         T0 Prescaler         PRE0           244 (F4)         Timer/Counter 0         T0           242 (F2)         Timer/Counter 1         T1           241 (F1H)         Timer Mode         TMR           128         Not Implemented         TMR           128         Registers         P3           4         Port 3         P3           2         Port 2         P2           1         Reserved         P1           0 (00H)         Port 0         P0 | Location  |                             | Identifiers |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------|-------------|

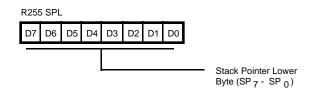

| 253 (FD)         Register Pointer         RP           252 (FC)         Program Control Flags         FLAGS           251 (FB)         Interrupt Mask Register         IMR           250 (FA)         Interrupt Request Register         IRQ           249 (F9)         Interrupt Priority Register         IPR           248 (F8)         Ports 0-1 Mode         P01M           247 (F7)         Port 3 Mode         P3M           246 (F6)         Port 2 Mode         P2M           245 (F5)         T0 Prescaler         PRE0           244 (F4)         Timer/Counter 0         T0           243 (F3)         T1 Prescaler         PRE1           242 (F2)         Timer/Counter 1         T1           241 (F1H)         Timer Mode         TMR           Not Implemented         TMR           128         127 (7FH)         General-Purpose Registers           4         3         Port 3         P3           2         Port 2         P2           1         Reserved         P1                                                                                                    | 255 (FFH) | Stack Pointer (Bits 7-0)    | SPL         |

| 252 (FC)         Program Control Flags         FLAGS           251 (FB)         Interrupt Mask Register         IMR           250 (FA)         Interrupt Request Register         IRQ           249 (F9)         Interrupt Priority Register         IPR           248 (F8)         Ports 0-1 Mode         P01M           247 (F7)         Port 3 Mode         P3M           246 (F6)         Port 2 Mode         P2M           245 (F5)         T0 Prescaler         PRE0           244 (F4)         Timer/Counter 0         T0           243 (F3)         T1 Prescaler         PRE1           242 (F2)         Timer/Counter 1         T1           241 (F1H)         Timer Mode         TMR           Not Implemented         TMR           128         127 (7FH)         General-Purpose Registers           4         3         Port 3         P3           2         Port 2         P2           1         Reserved         P1                                                                                                                                                           | 254 (FE)  | General-Purpose Register    | GPR         |

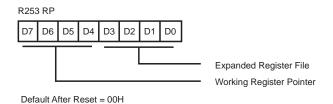

| 251 (FB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 253 (FD)  | Register Pointer            | RP          |

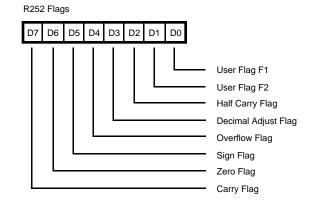

| 250 (FA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 252 (FC)  | Program Control Flags       | FLAGS       |

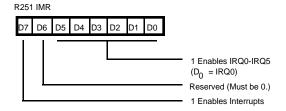

| 249 (F9)       Interrupt Priority Register       IPR         248 (F8)       Ports 0-1 Mode       P01M         247 (F7)       Port 3 Mode       P3M         246 (F6)       Port 2 Mode       P2M         245 (F5)       T0 Prescaler       PRE0         244 (F4)       Timer/Counter 0       T0         243 (F3)       T1 Prescaler       PRE1         242 (F2)       Timer/Counter 1       T1         241 (F1H)       Timer Mode       TMR         Not Implemented       Not Implemented         128       Port 3       P3         129       Port 2       P2         120       Port 2       P2         120       P1       Reserved       P1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 251 (FB)  | Interrupt Mask Register     | IMR         |

| 248 (F8)       Ports 0-1 Mode       P01M         247 (F7)       Port 3 Mode       P3M         246 (F6)       Port 2 Mode       P2M         245 (F5)       T0 Prescaler       PRE0         244 (F4)       Timer/Counter 0       T0         243 (F3)       T1 Prescaler       PRE1         242 (F2)       Timer/Counter 1       T1         241 (F1H)       Timer Mode       TMR         Not Implemented       TMR         128       Not Implemented         128       Port 3       P3         2       Port 3       P3         2       Port 2       P2         1       Reserved       P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250 (FA)  | Interrupt Request Register  | IRQ         |

| 247 (F7)       Port 3 Mode       P3M         246 (F6)       Port 2 Mode       P2M         245 (F5)       T0 Prescaler       PRE0         244 (F4)       Timer/Counter 0       T0         243 (F3)       T1 Prescaler       PRE1         242 (F2)       Timer/Counter 1       T1         241 (F1H)       Timer Mode       TMR         Not Implemented       TMR         128       Not Implemented         127 (7FH)       General-Purpose Registers         4       Port 3       P3         2       Port 2       P2         1       Reserved       P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 249 (F9)  | Interrupt Priority Register | IPR         |

| 246 (F6)       Port 2 Mode       P2M         245 (F5)       T0 Prescaler       PRE0         244 (F4)       Timer/Counter 0       T0         243 (F3)       T1 Prescaler       PRE1         242 (F2)       Timer/Counter 1       T1         241 (F1H)       Timer Mode       TMR         Not Implemented         128       Not Implemented         127 (7FH)       General-Purpose Registers         4       Port 3       P3         2       Port 2       P2         1       Reserved       P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 248 (F8)  | Ports 0-1 Mode              | P01M        |

| 245 (F5) T0 Prescaler PRE0 244 (F4) Timer/Counter 0 T0 243 (F3) T1 Prescaler PRE1 242 (F2) Timer/Counter 1 T1 241 (F1H) Timer Mode TMR  Not Implemented  128 127 (7FH)  General-Purpose Registers  4 3 Port 3 P3 2 Port 2 P2 1 Reserved P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 247 (F7)  | Port 3 Mode                 | P3M         |

| 244 (F4)       Timer/Counter 0       T0         243 (F3)       T1 Prescaler       PRE1         242 (F2)       Timer/Counter 1       T1         241 (F1H)       Timer Mode       TMR         Not Implemented         128       Not Implemented         127 (7FH)       General-Purpose Registers         4       Port 3       P3         2       Port 2       P2         1       Reserved       P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 246 (F6)  | Port 2 Mode                 | P2M         |

| 243 (F3)       T1 Prescaler       PRE1         242 (F2)       Timer/Counter 1       T1         241 (F1H)       Timer Mode       TMR         Not Implemented         128       Seneral-Purpose Registers         4       Port 3       P3         2       Port 2       P2         1       Reserved       P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 245 (F5)  | T0 Prescaler                | PRE0        |